# Verifying a Compiler Optimization for Multi-Threaded Java

Bernhard Reus, Alexander Knapp, Pietro Cenciarelli, and Martin Wirsing

Ludwig-Maximilians-Universität München {reus,knapp,cenciare,wirsing}@informatik.uni-muenchen.de

Abstract. The specification for the object-oriented concurrent language Java [3] is rather loose with respect to the interaction of shared memory and the local working memories of different threads. This allows maximal freedom in the language implementation. Such freedom is reflected in the semantics provided in [2], where threads-memory interaction is formalized in terms of structures called event spaces. Two kinds of memories are described in the Java specification: a "normal" memory and a more liberal one, where values can sometimes be stored even before they are produced as results of computation. Here we compare two structural operational semantics of a sublanguage of Java modelling the two types of memory. The two semantics share the same set of operational rules but put different requirements (expressed as first order theories) on the notion of event space. We prove a result which is informally stated in [3]: the two semantics coincide for properly synchronized programs. This shows the applicability of a new technique for combining structural operational semantics and first order specification of process behaviour.

#### 1 Introduction

A concurrent program consists of multiple tasks that are or behave as if they were executed all at the same time. Such tasks can be implemented using *threads* (short for "threads of execution"), which are sequences of instructions that run independently within the encompassing program. The object-oriented language Java supports thread programming (see e.g. [1], [4]).

Java threads share a common memory, but keep working copies of shared variables in private working memories. It is only when leaving a synchronized block that *must* a thread copy the content of its working memory in the main memory. However, possible implementations of the run-time system *may* choose to update the value of a variable in the main memory as soon as a thread makes an assignment to its working copy of that variable. The Java language specification [3] leaves freedom to the implementation in that respect.

A particular implementation technique is also discussed in [3], where a value can be stored by a thread in the main memory before such value is produced by the computation. This is called a *prescient* store action [3, §17.8]. The only restriction is that between the prescient store and the matching assignment nothing "bad" happens, e.g. no other thread reads illegitimately the prescient value. Consider the following code example.

```

o.b = 2;

for(o.a = 1; o.a < 10; o.a = o.a + 1)

o.b = o.a + o.b;

```

where o is (a reference to) an object with two attributes a and b of type int. When executed the value of o.a can only be stored after o.a has been assigned a new value, i.e. after it was incremented. If prescient store operations are permitted, then it would be also legal to store the value 10 for o.a in advance, i.e. before the loop is entered, excluding thereby that any other thread can load o.a before the end of the loop.

The rearrangement of store operations can be used to speed up programs when updating of variables is split into a thread action (called *Store*) and a memory action (*Write*). The global memory can concurrently provide the value of a pre-stored variable while a second thread waits for it. Re-grouping the store-operations might also optimize memory access itself.

In [2] we present a structural operational semantics (in the style of [5]) of a nontrivial sub-language of Java which includes dynamic creation of objects, blocks, and synchronization of threads. The notion of event space is introduced in that paper to formalize the communication protocol between shared memory and threads. Event spaces correspond roughly to configurations in Winskel's event structures [6], which are used for denotational semantics of concurrent languages.

Here we exploit the flexibility of the approach proposed in [2], where the operational semantics is given parametrically in the notion of event space, and compare two language implementations which share the same set of operational rules. The implementations are obtained by imposing different requirements on event spaces, so that prescient stores are possible in one case and impossible in the other. Such requirements are expressed in simple first order clauses. In this framework we prove that prescient and nonprescient semantics coincide for properly synchronized programs, that is programs where any two threads are not allowed to write a variable into the global memory without synchronization (race conditions [4]). This property was only informally stated in [3, §17.8]. We also provide an example where prescient store actions for non-properly synchronized programs lead to inconsistent memory contents.

The contribution of the paper is twofold: on the one hand it provides welcome formal confirmation of the intuitive correctness of certain compiler optimization techniques; on the other hand it shows the applicability of an innovative technique for combining structural operational semantics and first order axiomatisation of process behaviour.

The paper is organized as follows: Section 2 recapitulates the definition of event spaces from [2]. These are used in Section 3 for the SOS-rules. Next, the axiomatization of event spaces is changed (Section 4) in order to allow for prescient stores and prescient operational semantics is defined in Section 5. It is then proven, in Section 6, that for properly synchronized programs the extension is conservative w.r.t. the old semantics.

## 2 Event Spaces

The execution of a Java program comprises many threads of computation running in parallel. Threads exchange information by operating on values and objects residing in a shared main memory. As explained in the Java language specification [3], each thread also has a private working memory in which it keeps its own working copy of variables that it must use or assign. As the thread executes a program, it operates on these working copies. The main memory contains the master copy of each variable. There are rules about when a thread is permitted or required to transfer the contents of its working copy of a variable into the master copy or vice versa. Moreover, there are rules which regulate the locking and unlocking of objects, by means of which threads synchronize with each other. These rules are given in [3, Chapter 17] and have been formalized in [2] as "well-formedness" conditions for structures called event spaces. We summarize their definition and usage.

Event spaces will be included in the configurations of multi-threaded Java to constrain the applicability of certain operational rules. Additionally, they will be used to model the working memories of all threads. The main memory is modeled as an abstract store that can be thought of as mapping addresses of instance variables (left-values, from a semantic domain LVal) of objects (from a semantic domain Obj) to values or object references (right-values, from a semantic domain RVal).

In accord with [3], the terms *Use*, *Assign*, *Load*, *Store*, *Read*, *Write*, *Lock*, and *Unlock* are used here to name actions which describe the activity of the memories during the execution of a Java program. *Use* and *Assign* denote the above mentioned actions of the private working memory. *Read* and *Load* are used for a loosely coupled copying of data from the main memory to a working memory and dually *Store* and *Write* are used for copying data from a working memory to the main memory (as mentioned in the introduction).

We let the metavariable A (possibly indexed) stand for a generic action name. Moreover, we let B range over the set of thread actions and C over the set of memory actions, that is:  $B \in \{Use, Assign, Load, Store, Lock, Unlock\}, C \in \{Read, Write, Lock, Unlock\}.$

Let  $Thread\_id$  be a set of thread identifiers. An action is either a 4-tuple of the form  $(A, \theta, l, v)$  where  $A \in \{Assign, Store, Read\}$ ,  $\theta \in Thread\_id$ ,  $l \in LVal$  and  $v \in RVal$ , or a triple  $(A, \theta, l)$ , where  $\theta$  and l are as above and  $A \in \{Use, Load, Write\}$ , or a triple  $(A, \theta, o)$ , where  $A \in \{Lock, Unlock\}$  and  $o \in Obj$ .

Events are instances of actions, which we think of as happening at different times during execution. We use the same tuple notation for actions and their instances (the context clarifies which one is meant) and let a, b, c stand for either. Sometimes we omit components of an action or event: we may write e.g. (Read, l) for  $(Read, \theta, l, v)$  when  $\theta$  and v are not relevant.

An event space is a poset of events (thought of as occurring in the given order) in which every chain can be enumerated monotonically with respect to the arithmetical ordering  $0 \le 1 \le 2 \le \dots$  of natural numbers, and which satisfies the conditions (17.2.1–17.6.2') of Table 1. These conditions, which formalize directly

the rules of [3, Chapter 17], are expressed by clauses of the form:

$$\forall \boldsymbol{a} \in \eta . (\Phi \Rightarrow ((\exists \boldsymbol{b}_1 \in \eta . \Psi_1) \lor (\exists \boldsymbol{b}_2 \in \eta . \Psi_2) \lor \dots (\exists \boldsymbol{b}_n \in \eta . \Psi_n)))$$

where  $\boldsymbol{a}$  and  $\boldsymbol{b}_i$  are lists of events,  $\eta$  is an event space and  $\forall \boldsymbol{a} \in \eta$ .  $\Phi$  means that  $\Phi$  holds for all tuples of events in  $\eta$  matching the elements of  $\boldsymbol{a}$  (and similarly for  $\exists \boldsymbol{b} \in \eta$ .  $\Psi$ ). Such statements are abbreviated by adopting the following conventions: quantification over  $\boldsymbol{a}$  is left implicit when all events in  $\boldsymbol{a}$  appear in  $\Phi$ ; quantification over  $\boldsymbol{b}_i$  is left implicit when all events in  $\boldsymbol{b}_i$  appear in  $\Psi_i$ . Moreover, a rule of the form  $\forall \boldsymbol{a} \in \eta$ .  $(true \Rightarrow \ldots)$  is written  $\boldsymbol{a} \Rightarrow (\ldots)$ . The term  $(A, \theta, x)_n$  denotes the n-th occurrence of  $(A, \theta, x)$  in a given space, if such an event exists, and is undefined otherwise.

We include the origin of each rule from [3, Chapter 17] and refer to [3] and [2] for more detail. For instance, rule (17.2.1) says that actions performed by any thread are totally ordered and (17.2.2) that so are the actions performed by the main memory for any variable or object. Similarly, rules (17.6.2) and (17.6.2') say that a lock action acts as if it flushes all variables from the thread's working memory, i.e. before use they must be assigned or loaded from main memory.

A complete event space is an event space that additionally fulfills the axioms (17.2.6) and (17.2.7) such that any *Read* and *Store* events are "completed" by corresponding *Load* and *Write* events.

A new event  $a=(A,\theta,x)$  is adjoined to an event space  $\eta$  by extending the execution order as follows: if A is a thread action, then  $b\leq a$  for all instances b of  $(B,\theta)$  in  $\eta$ ; if a is a main memory action, then  $c\leq a$  for all instances c of (C,x) in  $\eta$ . Moreover, if A is Load then  $c\leq a$  for all instances c of  $(Read,\theta,x)$  in  $\eta$ , and if A is Write then  $c\leq a$  for all instances c of  $(Store,\theta,x)$  in  $\eta$ . The term  $\eta\oplus a$  denotes the space thus obtained, provided it obeys the above rules, and it is otherwise undefined. If it is defined then  $\eta\oplus a\downarrow$  yields true and false otherwise. If  $\eta$  is an event space and  $a=(a_1,a_2,\ldots a_n)$  is a sequence of events, we write  $\eta\oplus a$  for  $\eta\oplus a_1\oplus a_2\oplus\cdots\oplus a_n$  and analogously  $\eta\oplus a\downarrow$ .

## 3 Operational Semantics

We briefly recapitulate the structural operational semantics of multi-threaded Java in [2]. We restrict ourselves to those parts that are relevant for the "prescient" compiler optimization.

Objects are kept in the main memory. We use a semantic domain Store that is abstractly given by the following five semantic functions:  $upd: LVal \times RVal \times Store \rightarrow Store$  updates a given store; we write  $\mu[l \mapsto v]$  for  $upd(l, v, \mu)$ . The function  $lval: Obj \times Identifier \times Store \rightarrow LVal$  retrieves the left-value of an instance variable (such as of o.a). Analogously,  $rval: LVal \times Store \rightarrow RVal$  retrieves the right-value of a left-value; we write  $\mu(l)$  for  $rval(l, \mu)$ . New objects are allocated by  $new_C: Store \rightarrow Obj \times Store$ . This family of functions is indexed by class types  $C \in ClassType$ . For a given store  $\mu$ ,  $new_C(\mu)$  yields an object o and a store  $\mu'$  such that  $\mu'$  extends  $\mu$  where  $\mu'(lval(o,i,\mu'))$  is defined for any identifier i ranging over all instance variables of the class C.

$$(B,\theta), (B',\theta) \Rightarrow (B,\theta) \leq (B',\theta) \lor (B',\theta) \leq (B,\theta) \qquad (17.2.1)$$

$$(C,x), (C',x) \Rightarrow (C,x) \leq (C',x) \lor (C',x) \leq (C,x) \qquad (17.2.2)$$

$$(Assign,\theta,l) \leq (Load,\theta,l) \Rightarrow (Assign,\theta,l) \leq (Store,\theta,l) \leq (Load,\theta,l) \qquad (17.3.2)$$

$$(Store,\theta,l)_m < (Store,\theta,l)_n \Rightarrow \qquad (17.3.3)$$

$$(Store,\theta,l)_m \leq (Assign,\theta,l) \leq (Store,\theta,l)_n \qquad (17.3.4)$$

$$(Use,\theta,l) \Rightarrow (Assign,\theta,l) \leq (Use,\theta,l) \lor (Load,\theta,l) \leq (Use,\theta,l) \qquad (17.3.4)$$

$$(Store,\theta,l) \Rightarrow (Assign,\theta,l) \leq (Store,\theta,l) \qquad (17.3.5)$$

$$(Assign,\theta,l,v)_n \leq (Store,\theta,l,v') \Rightarrow \qquad (17.1)$$

$$v = v' \lor (Assign,\theta,l,v)_n < (Assign,\theta,l)_m \leq (Store,\theta,l,v')$$

$$(Load,\theta,l)_n \Rightarrow (Read,\theta,l)_n \leq (Load,\theta,l)_n \qquad (17.3.6)$$

$$(Write,\theta,l)_n \Rightarrow (Store,\theta,l)_n \leq (Write,\theta,l)_n \qquad (17.3.7)$$

$$(Store,\theta,l)_m \leq (Load,\theta,l)_n \Rightarrow (Write,\theta,l)_m \leq (Read,\theta,l)_n \qquad (17.3.8)$$

$$(Lock,\theta,o)_n \leq (Lock,\theta',o) \land \theta \neq \theta' \Rightarrow (Unlock,\theta,o)_n \leq (Lock,\theta',o) \qquad (17.5.1)$$

$$(Unlock,\theta,o)_n \Rightarrow (Lock,\theta,o)_n \leq (Unlock,\theta,o)_n \qquad (17.5.2)$$

$$(Assign,\theta,l) \leq (Unlock,\theta) \Rightarrow \qquad (Assign,\theta,l) \leq (Store,\theta,l)_n \leq (Write,\theta,l)_n \leq (Unlock,\theta)$$

$$(Lock,\theta) \leq (Use,\theta,l) \Rightarrow \qquad (17.6.1)$$

$$(Lock, \theta) \le (Store, \theta, l) \Rightarrow (Lock, \theta) \le (Assign, \theta, l) \le (Store, \theta, l)$$

(17.6.2)

(17.6.2)

$$(Read, \theta, l)_n \Rightarrow (Load, \theta, l)_n$$

$$(Store, \theta, l)_n \Rightarrow (Write, \theta, l)_n$$

$$(17.2.6)$$

Table 1. Event space axioms

$(Lock, \theta) < (Read, \theta, l)_n < (Load, \theta, l)_n < (Use, \theta, l)$

$(Lock, \theta) \le (Assign, \theta, l) \le (Use, \theta, l) \lor$

The local variables of a block are kept in a stack of environments. Environments, denoted Env, are pairs  $(I, \rho)$  of declared identifiers  $I \subseteq Identifier \cup \{this\}$ and a map  $\rho: I \longrightarrow RVal$  representing the values they (possibly) have. Environments are also used to store the information on which object's code is currently being executed  $(\rho(this))$ . An environment  $\rho$  is updated as usual by  $\rho[i \mapsto v]$ . The empty environment is denoted by  $\rho_{\emptyset}$ . Let S-Stack be the domain of (singlethreaded) stacks of environments. The empty stack is written  $\sigma_{\emptyset}$ . The operation  $push: Env \times S$ -Stack  $\rightarrow S$ -Stack is the usual one on stacks. We use the operations  $\sigma[i \mapsto v]$  for updating stacks, and  $\sigma(i)$  for retrieving values. Each thread of execution of a Java program has its own stack. We call M-Stack =  $Thread\_id \rightarrow S$ -Stack the domain of multi-threaded stacks, ranged over by  $\sigma$ . Given  $\sigma \in M$ -Stack, the multi-threaded stacks  $push(\theta, \rho, \sigma)$ ,  $\sigma[\theta, i \mapsto v]$  map  $\theta'$  to  $\sigma(\theta')$  when  $\theta \neq \theta'$ , and otherwise map  $\theta$  respectively to  $push(\rho, \sigma(\theta)), \ \sigma(\theta)[i \mapsto v]$ . Note that an additional operation is necessary for extending (stacks of) environments when dealing with local variable declarations, but those are not addressed in this paper (cf. [2]). We also write  $\sigma(\theta, i)$  instead of  $\sigma(\theta)(i)$ .

The operational semantics works on a set M-Term of multi-threaded abstract terms that contain single-threaded abstract terms from a set S-Term. We let the metavariable t range over S-Term. To each syntactic category of Java we associate a homonymous category of abstract terms. The well-typed terms of Java are mapped to abstract terms of corresponding category by a translation (\_)°, which we leave implicit when no confusion arises. Abstract blocks are terms of the form  $\{t\}_{(I,\rho)}$  where the source I of the environment  $(I,\rho)$  contains the local variables of the block. A multi-threaded abstract term T is a set of pairs  $(\theta,t)$ , where  $\theta \in Thread.id$  and  $t \in S$ -Term and no distinct elements of T bear the same thread identifier. Multi-threaded abstract terms  $\{(\theta_1,t_1),(\theta_2,t_2),\ldots\}$  are written as lists  $(\theta_1,t_1) \mid (\theta_2,t_2) \mid \ldots$  and pairs  $(\theta,t)$  are written t when  $\theta$  is irrelevant.

The configurations of multi-threaded Java are 4-tuples  $(T, \eta, \sigma, \mu)$  consisting of an M-term T, an event space  $\eta$ , an M-stack  $\sigma$ , and a store  $\mu$ . The operational semantics is the binary relation  $\longrightarrow$  on configurations inductively defined by the rules that follow. In the rule schemes in Tables 2–4, the metavariables range as follows:  $i \in Identifier$ ,  $k \in Identifier \cup LVal$ ,  $l \in LVal$ ,  $o \in Obj$ ,  $e \in Expression$ ,  $v \in RVal$ ,  $s \in Statement$ ,  $b \in BlockStatement$ , and  $b \in BlockStatement$ ,  $b \in BlockStatement$ , and  $b \in BlockStatement$ , and  $b \in BlockStatement$ , and  $b \in BlockStatement$ .

We write  $store_{\eta}(\theta, l)$  for the oldest unwritten value of l stored by  $\theta$  in  $\eta$ . More formally: let an event  $(Store, \theta, l)_n$  in  $\eta$  be called unwritten if  $(Write, \theta, l)_n$  is undefined in  $\eta$ ; then,  $store_{\eta}(\theta, l) = v$  if there exists an unwritten  $(Store, \theta, l, v)_n$  such that for any unwritten  $(Store, \theta, l)_m$  we have  $n \leq m$ ; if no such a Store event exists,  $store_{\eta}(\theta, l)$  is undefined. Similarly, we write  $rval_{\eta}(\theta, l)$  for the latest value of l assigned or loaded and read by  $\theta$  in  $\eta$ .

$$\begin{array}{lll} & \frac{e_1 \longrightarrow e_2}{e_1 = e \longrightarrow e_2 = e} & [assign2] & \frac{e_1 \longrightarrow e_2}{k = e_1 \longrightarrow k = e_2} \\ [assign3'] & (\theta, l = v), \eta \longrightarrow (\theta, v), \eta \oplus (Assign, \theta, l, v) \\ [assign4'] & (\theta, i = v), \sigma \longrightarrow (\theta, v), \sigma[\theta, i \mapsto v] \\ [binop1] & \frac{e_1 \longrightarrow e_2}{e_1 \text{ op } e \longrightarrow e_2 \text{ op } e} & [binop2] & \frac{e_1 \longrightarrow e_2}{v \text{ op } e_1 \longrightarrow v \text{ op } e_2} \\ [binop3] & v_1 \text{ op } v_2 \longrightarrow v_1 \text{ op } v_2 & [pth] & (e) \longrightarrow e \\ [access1] & \frac{e_1 \longrightarrow e_2}{e_1 \cdot i \longrightarrow e_2 \cdot i} & [access2] & o.i \cdot \mu \longrightarrow lval(o, i, \mu), \mu \\ [this] & (\theta, \text{this}), \sigma \longrightarrow (\theta, \sigma(\theta, this)), \sigma & [new] & \text{new } C (), \mu \longrightarrow new_C(\mu) \\ [val'] & (\theta, l), \eta \longrightarrow (\theta, rval_{\eta}(\theta, l)), \eta \oplus (Use, \theta, l) \\ [var'] & (\theta, i), \sigma \longrightarrow (\theta, \sigma(\theta, i)), \sigma \end{array}$$

Table 2. Expressions

$$[\text{statseq1}] \quad \frac{b_1 \longrightarrow b_2}{b_1 B \longrightarrow b_2 B} \qquad [\text{statseq2}] \quad \frac{b, \mu_1 \longrightarrow \mu_2}{b B, \mu_1 \longrightarrow B, \mu_2}$$

$$[\text{expstat1}] \quad \frac{e_1 \longrightarrow e_2}{e_1; \longrightarrow e_2;} \qquad [\text{expstat2}] \quad \frac{e, \mu_1 \longrightarrow v, \mu_2}{e; , \mu_1 \longrightarrow \mu_2}$$

$$[\text{skip}] \quad ; , \sigma \longrightarrow \sigma \qquad [\text{block1}] \qquad \{\ \}_{\rho}, \sigma \longrightarrow \sigma$$

$$[\text{block2'}] \quad \frac{(\theta, B_1), push(\theta, \rho_1, \sigma_1) \longrightarrow (\theta, B_2), push(\theta, \rho_2, \sigma_2)}{(\theta, \{B_1\}_{\rho_1}), \sigma_1 \longrightarrow (\theta, \{B_2\}_{\rho_2}), \sigma_2}$$

$$[\text{if1}] \quad \frac{e_1 \longrightarrow e_2}{\text{if}(e_1) \ s \longrightarrow \text{if}(e_2) \ s}$$

$$[\text{if2}] \quad \text{if}(true) \ s \longrightarrow s \quad [\text{if3}] \quad \text{if}(false) \ s, \mu \longrightarrow \mu$$

$$[\text{while}] \quad \text{while}(e) \ s \longrightarrow \text{if}(e) \ \{\ s \text{ while}(e) \ s\ \}$$

$$[\text{for}] \quad \text{for}(e_1; \ e_2; \ e_3) \ s \longrightarrow \{\ e_1; \ \text{while}(e_2) \ \{\ s \ e_3; \ \}\ \}$$

Table 3. Statements

$$\begin{array}{c} & \underbrace{e_1 \longrightarrow e_2} \\ & \text{synchronized}(e_1) \ q \longrightarrow \text{synchronized}(e_2) \ q \\ \\ & \underbrace{q_1 \longrightarrow q_2} \\ & \text{synchronized}(o) \ q_1 \longrightarrow \text{synchronized}(o) \ q_2 \\ \\ & \underbrace{(\theta,e),\eta_1 \longrightarrow (\theta,o),\eta_2} \\ & \underbrace{(\theta,\text{synchronized}(e) \ q),\eta_1 \longrightarrow (\theta,\text{synchronized}(o) \ q),\eta_2 \oplus (Lock,\theta,o)} \\ & \text{[unlock]} & (\theta,\text{synchronized}(o) \ \{ \ \}_{\rho}),\eta \longrightarrow \eta \oplus (Unlock,\theta,o) \\ \\ & \text{[read]} & T,\eta,\mu \longrightarrow T,\eta \oplus (Read,\theta,l,\mu(l)),\mu \\ \\ & \text{[load]} & T,\eta \longrightarrow T,\eta \oplus (Load,\theta,l) \\ \\ & \text{[store]} & T,\eta \longrightarrow T,\eta \oplus (Store,\theta,l,v) \\ \\ & \text{[write]} & T,\eta,\mu \longrightarrow T,\eta \oplus (Write,\theta,l),\mu[l \mapsto store_{\eta}(\theta,l)] \\ \\ & \underbrace{t_1 \longrightarrow t_2} \\ t_1 \mid T \longrightarrow t_2 \mid T \\ \\ \end{array}$$

Table 4. Multi-threaded Java

The rules [assign3', val', lock, unlock, read, load, store, write] make use of the well-formedness conditions of event spaces via the  $\oplus$ . The rules [read, load, store, write] are spontaneous in the sense that they do not depend on T. The [store] rule additionally "guesses" the value of the last Assign; its correctness is ensured by axiom (17.1). Synchronization, i.e. mutual exclusion, is handled by [synchro1, synchro2, lock, unlock], by [par] sequential computations are lifted to multi-threaded ones.

### 4 Prescient Event Spaces

The prescient store actions are introduced in [3, 17.8] as follows: "... the store [of variable V by thread T] action [is allowed] to instead occur before the assign action, if the following rule restrictions are obeyed:

- If the *store* occurs, the *assign* is bound to occur. . . .

- No lock action intervenes between the relocated store and the assign.

- No load of V intervenes between the relocated store and the assign.

- No other store of V intervenes between the relocated store and the assign.

- The store action sends to the main memory the value that the assign action will put into the working memory of thread T.

The last property inspires us to call such an early store action prescient: ... "

The specification above seems to assume that it is known which *Store* events are prescient and which prescient *Store* event is matched by which *Assign* event. We do not assume such knowledge but adopt a more general approach introducing so-called complete labellings. These labellings are not necessarily unique but it is always possible to infer a complete labelling at run time. It will turn out, however, that the semantics is independent of the choice of complete labellings, see Corollary 6.

In order to define the new prescient event spaces we proceed as follows:

First, we have to add new relations (cf. axioms (17.2.1), (17.2.2)) between certain actions of different threads in order to be able to formalize the preconditions of the second, third, and fourth requirement above. Assign, Load or Store actions for the same variable and Lock actions must be comparable. To this end let  $D = \{Assign, Load, Store\}$ , then we stipulate:

$$(D, \theta, l), (D, \theta', l) \Rightarrow (D, \theta, l) \leq (D, \theta', l) \vee (D, \theta', l) \leq (D, \theta, l)$$

Since Store and Lock events are already comparable, by transitivity also Lock and D actions are comparable.

Second, rules (17.3.3), (17.3.5), (17.1), and (17.6.2') are now used for the definition of a predicate *prescient* on event spaces and *Store* events yielding true iff a *Store* is necessarily prescient. We define  $prescient_{\eta}((Store, \theta, l)_n)$  to be valid if one of the rules in Table 5 holds. Note that  $\eta$  is usually omitted if it is clear from the context.

Rules (P1-P4) simply tell that a *Store* event which does not obey old rules (17.3.3), (17.3.5), (17.1), or (17.6.2') is necessarily prescient. Rule (P5) is sound because if there is only one  $(Assign, \theta, l, v)$  between two stores and the first is *prescient*, then by re-arranging the prescient *Store* two *Store* events would follow each other without a triggering Assign in between, which contradicts the old semantics.

Third, keep rules (17.2.1), (17.2.2), (17.3.4), (17.3.6), (17.3.7), (17.3.8), (17.5.1), (17.5.2), and (17.6.2).

$$(Store, \theta, l)_m \le (Store, \theta, l)_n \Rightarrow (Store, \theta, l)_m \le (Assign, \theta, l) \le (Store, \theta, l)_n$$

(P1)

$$(Store, \theta, l)_n \not\Rightarrow (Assign, \theta, l) \le (Store, \theta, l)_n$$

(P2)

$$(Assign, \theta, l, v')_m \le (Store, \theta, l, v)_n \Rightarrow v = v' \lor (Assign, \theta, l, v')_m < (Assign, \theta, l)_k \le (Store, \theta, l, v)_n$$

(P3)

$$(Lock, \theta) \le (Store, \theta, l)_n \not\Rightarrow (Lock, \theta) \le (Assign, \theta, l) \le (Store, \theta, l)_n \tag{P4}$$

$$(Store, \theta, l)_m \le (Assign, \theta, l)_k \le (Assign, \theta, l)_{k'} \le (Store, \theta, l)_n \land prescient((Store, \theta, l)_m) \Rightarrow k = k'$$

(P5)

Table 5. Rules for prescient

Fourth, adapt rule (17.3.2) as follows, allowing prescient *Stores* on the right hand side of an implication:

$$\begin{split} (Assign, \theta, l, v) &\leq (Load, \theta, l) \Rightarrow \\ &((Assign, \theta, l) \leq (Store, \theta, l) \leq (Load, \theta, l)) \vee \\ &((Store, \theta, l, v) \leq (Assign, \theta, l, v) \leq (Load, \theta, l) \wedge prescient(Store, \theta, l, v)) \end{split}$$

and rule (17.6.1) as follows:

$$(Assign, \theta, l, v) \leq (Unlock, \theta) \Rightarrow$$

$$(Assign, \theta, l) \leq (Store, \theta, l)_n \leq (Write, \theta, l)_n \leq (Unlock, \theta)) \vee$$

$$((Store, \theta, l, v)_n \leq (Assign, \theta, l, v) \leq (Unlock, \theta) \wedge$$

$$(Write, \theta, l)_n \leq (Unlock, \theta) \wedge prescient((Store, \theta, l, v)_n))$$

Finally, we need an additional rule corresponding to the second, third, and fourth requirements in the citation at top of Section 4. We add a new rule scheme: for any  $a \in \{(Lock), (Load, l), (Store, l)\}$ :

$$(Store, \theta, l, v)_n < a \land prescient((Store, \theta, l, v)_n) \Rightarrow (Store, \theta, l, v)_n \leq (Assign, \theta, l, v) \leq a$$

$$(17.8)$$

Next, we redefine the operation  $\oplus$  on prescient event spaces: A new event a is adjoined to a prescient event space  $\eta$  as in the case for old event spaces, but one additional condition. Let  $A \in \{Store, Assign, Load\}$ . If  $a = (A, \theta, l)$  and  $b = (A, \theta', l) \in \eta$  then  $b \leq a$ . Also, the term  $\eta \oplus a$  denotes the space thus obtained, provided it obeys the above rules for prescient event spaces, and it is otherwise undefined.

Analogously to the predicate prescient one can also define a predicate  $non\_prescient$  which contains only Stores that are necessarily non-prescient. We define  $non\_prescient((Store, \theta, l)_m)$  on an (implicitly) given event space to be true if one of the rules of Table 6 is fulfilled.

Rule (NP2) is the dual of (P5). Moreover, rule (NP2) is raised by (17.3.3) and (NP3) by new rule (17.8). Observe also that the predicate *prescient* propagates from past to present whereas  $non\_prescient$  is computed in the opposite direction. Note that  $\neg non\_prescient(B)$  is not equivalent to prescient(B)

$$\neg \exists (Assign, \theta, l, v) . (Store, \theta, l)_m \le (Assign, \theta, l, v)$$

(NP1)

$$(Store, \theta, l)_m \le (Assign, \theta, l)_k \le (Assign, \theta, l)_{k'} \le (Store, \theta, l)_n \land non\_prescient((Store, \theta, l)_n) \Rightarrow k = k'$$

(NP2)

$$\forall a \in \{(Lock), (Load, l), (Store, l)\} . (Store, \theta, l, v)_m < a \Rightarrow \\ \neg \exists (Assign, \theta, l, v) . (Store, \theta, l, v)_m \le (Assign, \theta, l, v) \le a$$

(NP3)

Table 6. Rules for non\_prescient

and hence also  $prescient(B) \lor non\_prescient(B)$  does not always hold and  $prescient(B) \land non\_prescient(B)$  is not always false.

A prescient event space  $\eta$  is called  $consistently\ complete$  if it is complete and for no instance of a Store, say s, we have that  $prescient_{\eta}(s) \wedge non\_prescient_{\eta}(s)$ . Note that it makes only sense for the final event space of a reduction sequence to be consistently complete (as for complete). During execution, the matching Assign for a prescient Store might not have happened and therefore the corresponding Store would be considered  $non\_prescient$ , which might lead to a contradiction. A consistently complete event space fulfills the first and last requirement in [3, §17.8] (see top of Section 4), because a prescient Store would otherwise have no matching Assign and hence by rule (NP1) contradict consistently completeness.

There might be a Store event s in a given event space for which neither prescient(s) nor  $non\_prescient(s)$  is derivable. In this case one needs a "labelling" of Store events, i.e. a predicate fixing whether a Store shall be considered prescient or not. More formally, a labelling for a prescient event space is a predicate  $\ell$  on Store events such that it obeys rules (L1–L3) in Table 7.

$$prescient(s) \Rightarrow \ell(s)$$

(L1)

$$non\_prescient(s) \Rightarrow \neg \ell(s)$$

(L2)

$$((Store, \theta, l)_m \le (Assign, \theta, l)_k \le (Assign, \theta, l)_{k'} \le (Store, \theta, l)_n \Rightarrow k = k') \Rightarrow (\ell((Store, \theta, l)_m)) \Rightarrow \ell((Store, \theta, l)_n))$$

(L3)

$$prescient(s) \Rightarrow p^*(s)$$

(PC1)

$$p(s) \Rightarrow p^*(s)$$

(PC2)

$$((Store, \theta, l)_m \le (Assign, \theta, l)_k \le (Assign, \theta, l)_{k'} \le (Store, \theta, l)_n \Rightarrow k = k') \Rightarrow (p^*((Store, \theta, l)_m) \Rightarrow p^*((Store, \theta, l)_n))$$

(PC3)

**Table 7.** Rules for labelling and prescient closure

Rule (L3) implies that  $\neg \ell$  is closed under (NP2).

Let p be any binary predicate on event spaces and *Store* events (where we usually omit the event space argument). Then we define the *prescient closure* of p, the binary predicate  $p^*$ , inductively by rules (PC1-PC3) of Table 7.

Lemma 1. For any consistently complete event space one can give a labelling.

*Proof.* Choose a p such that  $\neg(p(s) \land non\_prescient(s))$  holds for any *Store* event s. This is possible since the event space is consistently complete; for example, p = prescient (or equivalently p = false) will do. It remains to prove that  $p^*$  is a labelling: rules (L1) and (L3) hold by (PC1) and (PC3), respectively. In order to show rule (L2) prove by induction on the derivation of  $p^*(s)$  that  $non\_prescient(s) \land p^*(s)$  leads to a contradiction. In the (PC1)-case one needs consistently completeness and in the (PC2)-case the assumption on p.

For a consistently complete prescient event space with a labelling the Assign events matching the prescient Stores can also be singled out as follows: Let  $\ell$  be a labelling on an prescient event space  $\eta$ . A matching (labelling of Assigns) on  $\ell$  and  $\eta$ ,  $m_{\ell_{\eta}}$  is a predicate on the Assign events of  $\eta$  fulfilling the three axioms in Table 8.

```

\forall a \in \{(Lock), (Load, l), (Store, l)\} . (Store, \theta, l, v) < a \land \ell((Store, \theta, l, v)) \Rightarrow \\ (Store, \theta, l, v) \leq (Assign, \theta, l, v) \leq a \land m_{\ell}((Assign, \theta, l, v)) \\ (Store, \theta, l, v) \land \ell((Store, \theta, l, v)) \Rightarrow \\ (Store, \theta, l, v) \leq (Assign, \theta, l, v) \land m_{\ell}((Assign, \theta, l, v)) \\ (Store, \theta, l, v)_{k} \leq (Assign, \theta, l, v)_{m} < (Assign, \theta, l, v)_{n} \land \\ \ell((Store, \theta, l, v)_{k}) \land m_{\ell}((Assign, \theta, l, v)_{m}) \land m_{\ell}((Assign, \theta, l, v)_{n}) \Rightarrow \\ (Store, \theta, l, v)_{k} \leq (Assign, \theta, l, v)_{m} \leq (Store, \theta, l, v)_{k'} \leq (Assign, \theta, l, v)_{n} \land \\ \ell((Store, \theta, l, v)_{k'})

```

Table 8. Rules for matching

It is easily checked that the following predicate fulfills the axioms for matchings.

```

\begin{split} \hat{m}_{\ell}((Assign,\theta,l,v)_m) &\Leftrightarrow \\ &\exists (Store,\theta,l,v). \, (Store,\theta,l,v) \leq (Assign,\theta,l,v)_m \wedge \ell((Store,\theta,l,v)) \wedge \\ &\neg \exists (Assign,\theta,l,v)_n \, . \, (Store,\theta,l,v) \leq (Assign,\theta,l,v)_n < (Assign,\theta,l,v)_m \end{split}

```

A complete labelling is a pair consisting of a labelling and a matching for this labelling.

For the sake of simplicity we assume in the rest of the paper that a complete labelling is always given and exhibited in form of special action names, i.e. pStore and pAssign. If  $prescient(Store, \theta, l, v)$  holds then  $(Store, \theta, l, v)$  is denoted  $(pStore, \theta, l, v)$  and analogously for the matching Assign we use pAssign.

## 5 Prescient Operational Semantics

We obtain the prescient operational semantics from the old semantics of Section 3 just by switching from the event spaces of Section 2 to the prescient event spaces of Section 4 keeping the operational rules untouched.

For the prescient operational semantics we write  $\longrightarrow$ . Moreover, let  $Conf_{\triangleright}$  denote the set of configurations with prescient event spaces, and  $Conf_{\triangleright}$  those according to the definition  $\longrightarrow$  of Section 2.

**Lemma 2.** Any event space  $\eta$  (obeying the old rules) is also a prescient event space, thus any old configuration is a new configuration, i.e.  $Conf_{\triangleright} \subseteq Conf_{\triangleright}$ , and any reduction  $\Gamma \longrightarrow \Gamma'$  is also a prescient one, i.e.  $\Gamma \longrightarrow \Gamma'$  holds as well.

*Proof.* Assume  $\eta$  is an event space satisfying the old rules. By a simple induction,  $prescient_{\eta}(s)$  never holds for any Store event s in  $\eta$ . Thus  $\eta$  is a prescient event space because the new rules form a subset of the old rules. Since the configurations only differ in the event space definition and the rules of the semantics are not changed at all, the other claims of the lemma now hold trivially.

Since we use labellings our operational semantics is very liberal. It accepts reductions using Store events even if it is not clear during execution whether this Store event is meant to be prescient or not. In such a case, however, the prescient Store is not done as early as possible. Therefore, in practical cases, any Store which is not immediately recognized by the rules (P1–P5) can be considered nonprescient. This corresponds to the prescient closure  $false^*$  (cf. Lemma 1) meaning that the labelling is computed at run time. By definition also  $\hat{m}_{false^*}$  is computable at run time, thus a complete labelling is, too.

#### 6 Prescient Semantics is conservative

The relation between the "normal" and the "prescient" semantics is described in [3, §17.8] as follows: "The purpose of this relaxation is to allow optimizing Java compilers to perform certain kinds of code rearrangements that preserve the semantics of properly synchronized programs but might be caught in the act of performing memory actions out of order by programs that are not properly synchronized."

This has to be formalized in the sequel. The following notation, exemplified for  $\longrightarrow$  only, will be used analogously for all kinds of arrows:  $\stackrel{r}{\longrightarrow}$  denotes a one-step reduction with rule r; if  $e = (r_1, \ldots, r_n)$  is a list of rules then  $\stackrel{\epsilon}{\longrightarrow}$  denotes  $\stackrel{r_1}{\longrightarrow} \ldots \stackrel{r_n}{\longrightarrow}$ ; if the list is irrelevant we write  $\longrightarrow^*$ . For rules that change the event space we often decorate arrows with actions instead of rule names as the latter are ambiguous.

First, we observe that  $\longrightarrow$  and  $\longrightarrow$  can not be bisimilar by definition since  $\longrightarrow$  permits Store-actions where  $\longrightarrow$  does not. But  $\longrightarrow$  cannot even be bisimilar to the reflexive closure of  $\longrightarrow$ , since simulating a  $(pStore, \theta, l)$  and the following Writes by void steps leads to inequivalent configurations (since the main memories will contain different values for l).

As a prerequisite for a simulation relation of type  $Conf_{\triangleright} \times Conf_{\triangleright}$ , we define an equivalence on prescient configurations  $\sim \subseteq Conf_{\triangleright} \times Conf_{\triangleright}$  as follows:

$$(T, \eta, \sigma, \mu) \sim (T', \eta', \sigma', \mu') \Longleftrightarrow T = T' \land \sigma = \sigma' \land (T, \eta, \sigma, \mu) \downarrow (T', \eta', \sigma', \mu')$$

$$(T, \eta, \sigma, \mu) \downarrow (T', \eta', \sigma', \mu') \Longleftrightarrow \forall \boldsymbol{a} \cdot \eta \oplus \boldsymbol{a} \downarrow \Leftrightarrow \eta' \oplus \boldsymbol{a} \downarrow \land$$

$$\forall e \cdot (T, \eta, \sigma, \mu) \stackrel{e}{\Longrightarrow} (T_1, \eta_1, \sigma_1, \mu_1) \land (T', \eta', \sigma', \mu') \stackrel{e}{\Longrightarrow} (T_2, \eta_2, \sigma_2, \mu_2) \Rightarrow \mu_1 = \mu_2$$

where a is any sequence of actions, e is a sequence of rules and  $(T, \sigma, \eta, \mu) \longrightarrow^{c} (T', \sigma', \eta', \mu')$  if  $(T, \sigma, \eta, \mu) \longrightarrow^{*} (T', \sigma', \eta', \mu')$  such that  $\eta'$  is complete.

This equivalence relation is obviously preserved by the rules of the semantics:

**Lemma 3.** The relation  $\sim$  is an equivalence relation such that if  $\Gamma_1 \sim \Gamma_2$  then  $\Gamma_1 \xrightarrow{r} \Gamma_1'$  iff  $\Gamma_2 \xrightarrow{r} \Gamma_2'$  for any rule r, and if such a reduction r exists then  $\Gamma_1' \sim \Gamma_2'$  holds.

In order to establish a bisimulation result, we must delay all the operations which are possible due to a  $(pStore, \theta, l, v)$  until the matching pAssign event.

But that will not work for all kinds of programs. Consider the following example:

$$(\theta, \{ \text{synchronized}(o) \{ l = v; \}_{\rho_{\theta}} \}_{\rho_{\theta}}) \mid (\theta', \{ l = v'; \}_{\rho_{\theta}})$$

Its execution may give rise to a sequence of computation steps which contains the following complete subsequence of actions:

$$(Lock, \theta, o), (Assign, \theta, l, v), (Store, \theta, l, v), (pStore, \theta', l, v'),$$

$(Write, \theta', l), (Write, \theta, l), (Unlock, \theta, o), (pAssign, \theta', l, v')$

In a simulation the  $(Store, \theta', l, v')$  is illegal w.r.t. to the old event space definition and can only be simulated by a void (i.e. delaying) step as well as the following Write. Now the  $(Write, \theta, l)$  is bound to occur before the Unlock and therefore also  $(Store, \theta, l, v)$ . Finally, after the Assign we must recover the pending prescient  $(Store, \theta', l, v')$  and its corresponding  $(Write, \theta', l)$ . According to this simulation l has value v' in the global memory, but the reduction via  $\longrightarrow$  yields v for l. Thus, both end-configurations are not equivalent, a contradiction.

Therefore, we have to restrict ourselves to "properly synchronized" programs. A multi-threaded program T is called properly synchronized if for any configuration  $(T', \eta', \sigma', \mu')$  such that  $(T, \eta, \sigma_{\emptyset}, \emptyset) \longrightarrow^* (T', \eta', \sigma', \mu')$  and  $(Write, \theta_1, l, v_1) \leq (Write, \theta_2, l, v_2)$  in  $\eta'$  there is a  $(Lock, \theta_3, o)$  in  $\eta'$  such that  $(Write, \theta_1, l, v_1) \leq (Lock, \theta_3, o) \leq (Write, \theta_2, l, v_2)$ . To be "properly synchronized" is a semantical (and rather intricate) property which for a program is hard to tell in advance. A sufficient condition for "properly synchronizedness" is the syntactic criterion that in a program shared variables may only be written in synchronized blocks. It is clear, that in any execution sequence two Write actions must then be separated by the corresponding Lock.

In the sequel  $\Delta$  (possibly with annotations) stands for configurations in  $Conf_{\bullet}$  and  $\Gamma$  for new configurations in  $Conf_{\bullet}$ . Recall that any old configuration is also a valid one in the new sense by Lemma 2. According to the observations above, we define a new reduction relation  $\Longrightarrow$ :  $(Conf_{\bullet} \times E^*) \times (Conf_{\bullet} \times E^*)$  where  $E = \{(pStore), (Write), (Read)\}$  by the rules of Table 6. Note that we do not need to treat (Load) events (cf. rule (17.8)). The corresponding  $\Longrightarrow$ -configurations  $(\Delta, e)$  consist of an old configuration  $\Delta \in Conf_{\bullet}$  plus a list of "pending" events e. Appending an event e at the end of a list e is written  $e \circ a$ . An additional operation  $split_{\theta,l}(e)$  is needed. Given a list of events e it yields a

pair of lists  $(e_l, e')$  where both are sublists of e;  $e_l$  is obtained from e by extracting all  $(pStore, \theta, l)$ ,  $(Write, \theta, l)$  and  $(Read, \theta', l)$  events simultaneously changing a  $(pStore, \theta, l)$  into  $(Store, \theta, l)$ , and e' is  $e_l$ 's complement w.r.t. e.

$$(\Delta, e) \stackrel{(pStore, \theta, l, v)}{\longleftrightarrow} (\Delta, e \circ (pStore, \theta, l, v))$$

(red<sub>s</sub>)

$$(\Delta, e) \stackrel{(Write, \theta, l)}{\longmapsto} (\Delta, e \circ (Write, \theta, l)) \quad \text{if} \quad (pStore, \theta, l, v) \in e \quad (red_w)$$

$$(\Delta, e) \overset{(Read, \theta', l, v)}{\longrightarrow} (\Delta, e \circ (Read, \theta', l, v)) \quad \text{if} \quad (Write, \theta, l) \in e \qquad (\text{red}_r)$$

$$(\Delta, e) \stackrel{(pAssign, \theta, l, v)}{\longleftarrow} (\Delta', e') \quad \text{if} \quad split_{\theta, l}(e) = (e_l, e') \land \\ \Delta \stackrel{(Assign, \theta, l, v)}{\longleftarrow} \Delta_1 \stackrel{e_l}{\longrightarrow} \Delta'$$

(red<sub>a</sub>)

$$(\Delta, e) \stackrel{r}{\rightarrowtail} (\Delta', e)$$

for any other case  $r$  if  $\Delta \stackrel{r}{\longrightarrow} \Delta'$  (red<sub>d</sub>)

Table 9. Rules for the simulating reduction relation

To relate configurations of  $\longrightarrow$  and  $\rightarrowtail$  reductions the simulation relation  $\approx \subseteq Conf_{\triangleright} \times (Conf_{\triangleright} \times E^*)$  is defined as follows:

$$\Gamma \approx (\Delta, e)$$

if, and only if,  $\Delta \stackrel{e}{\longrightarrow} \Gamma_{\Delta} \wedge \Gamma_{\Delta} \sim \Gamma$

i.e.  $\Gamma$  is equivalent to  $(\Delta, e)$  if  $\Gamma$  is equivalent to the completion of  $\Delta$ , usually called  $\Gamma_{\Delta}$ , by executing the pending events in e. Note that  $\Longrightarrow$  is used here for the sequence of events e, as e may contain prescient Store events.

Below we use the following notation of a commuting diagram

$$\begin{array}{ccc}

\Gamma & \longrightarrow & \Gamma_1 \\

\downarrow & \sim & \downarrow \\

\Gamma_3 & \longrightarrow & \Gamma_2

\end{array}$$

stating that  $\Gamma \longrightarrow \Gamma_1 \longrightarrow \Gamma_2$  and  $\Gamma \longrightarrow \Gamma_3 \longrightarrow \Gamma_2'$  and  $\Gamma_2 \sim \Gamma_2'$ . This notation is also used for any other kind of arrows.

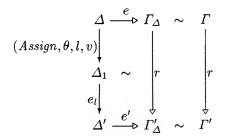

**Lemma 4.** If  $\Gamma \approx (\Delta, e)$  and  $\Gamma \xrightarrow{r} \Gamma'$ , where r is as in case  $(\text{red}_d)$  and  $\Gamma$  stems from a properly synchronized program, then  $\Delta \xrightarrow{r} \Delta'$  and the diagram

$$\begin{array}{cccc}

\Delta & \xrightarrow{e} & \Gamma_{\Delta} & \sim & \Gamma \\

\downarrow^r & r \downarrow & & \downarrow^r \\

\Delta' & \xrightarrow{e} & \Gamma'_{\Delta} & \sim & \Gamma'

\end{array}$$

commutes, hence in particular  $\Gamma \approx (\Delta, e) \stackrel{r}{\rightarrowtail} (\Delta', e) \approx \Gamma'$  holds.

*Proof.* (sketched) By definition of  $\rightarrowtail$  we have  $\Delta \xrightarrow{r} \Delta'$  as we consider case (red<sub>d</sub>). Next, we have to check that r does not depend on e, such that commutation is possible. Proof is by inspecting the relevant laws for event spaces: rules

(17.3.2), (17.3.4), (17.6.2) refer to *Load* events which are not possible as long as e contains a corresponding pStore, (17.3.7) is not relevant as matching Writes are treated in  $(red_w)$ . Thus, we are left with (17.6.1). Cases, however, where Store and Write in e allow r to be an Unlock are excluded by the rules for labellings.

To prove that the diagram commutes it suffices by definition of  $\sim$  to show that the same actions are executed, but maybe in different order. We have to ensure that Write events of the same variable from different threads are not re-ordered. But this could only happen if  $r = (Write, \theta, l)$  and another  $(Write, \theta', l) \in e$  which is impossible since only properly synchronized programs are considered.

**Theorem 5.** For properly synchronized programs the relation  $\approx$  is a simulation relation of  $\longrightarrow$  and  $\rightarrowtail$ , i.e. if  $\Gamma \stackrel{r}{\longrightarrow} \Gamma'$  during the execution of such a program and  $\Gamma \approx (\Delta, e)$  then there is a  $(\Delta', e')$  such that  $(\Delta, e) \stackrel{r}{\rightarrowtail} (\Delta', e')$  and  $\Gamma' \approx (\Delta', e')$ .

*Proof.* Assume  $\Gamma \approx (\Delta, e)$ , i.e.  $\Delta \stackrel{e}{\longrightarrow} \Gamma_{\Delta} \sim \Gamma$ . We do a case analysis for  $\Gamma \stackrel{r}{\longrightarrow} \Gamma'$ :  $Case \ \Gamma \stackrel{Write}{\longrightarrow} \Gamma'$ : if  $(pStore, \theta, l) \in e$  then it holds that  $(\Delta, e) \stackrel{r}{\rightarrowtail} (\Delta, e \circ r)$  by  $(red_w)$ . Moreover, by Lemma 3,  $\Gamma' \approx (\Delta, e \circ r)$ .

If  $(pStore, \theta, l) \notin e$  then by Lemma 4,  $(\Delta, e) \stackrel{r}{\longmapsto} (\Delta', e')$  and  $\Gamma' \approx (\Delta', e)$ . Case  $\Gamma \stackrel{pAssign}{\Longrightarrow} \Gamma'$ . Let  $split_{\theta,l}(e) = (e_l, e')$ . Since an Assign is always possible, assume that  $\Delta \stackrel{(Assign, \theta, l, v)}{\Longrightarrow} \Delta_1$ . Now every action in  $e_l$  becomes legal for the old semantics, so we can further assume  $\Delta_1 \stackrel{e_l}{\Longrightarrow} \Delta'$ , such that  $(\Delta, e) \stackrel{r}{\Longrightarrow} (\Delta', e')$ . One can prove analogously to Lemma 4 that the left rectangle in

commutes; the right rectangle commutes by Lemma 3, thus  $(\Delta, e) \stackrel{r}{\rightarrowtail} (\Delta', e')$  and  $\Gamma' \approx (\Delta', e')$ .

For pStore and Read one proceeds as for Write, all other cases follow from Lemma 4.

Our main result is the following corollary which states that the prescient semantics is conservative, i.e. any prescient execution sequence of a properly synchronized program can be simulated by a "normal" execution of Java.

**Corollary 6.** Given  $\Gamma \in Conf_{\triangleright}$  from a properly synchronized program and  $\Delta \in Conf_{\triangleright}$ , if  $\Gamma \sim \Delta$  and  $\Gamma \longrightarrow^* \Gamma'$  such that the event space  $\eta_{\Gamma'}$  of  $\Gamma'$  is consistently

complete, then for any complete labelling of  $\eta_{\Gamma'}$  there is a reduction sequence  $\Delta \longrightarrow^* \Delta'$  such that  $\Gamma' \sim \Delta'$ .

Moreover, if two different complete labellings yield two different reduction sequences  $\Delta \longrightarrow^* \Delta_1'$  and  $\Delta \longrightarrow^* \Delta_2'$ , then still  $\Delta_1' \sim \Delta_2'$  holds.

*Proof.* First, observe that if  $\Gamma \sim \Delta$  then  $\Gamma \approx (\Delta, \varepsilon)$ . By a simple induction on the length of the derivation by Theorem 5, we get  $(\Delta, \varepsilon) \rightarrowtail^* (\Delta', e)$  and  $\Gamma' \approx (\Delta', e)$ . Now  $e = \varepsilon$  follows from the fact that  $\Gamma'$  is consistently complete which entails that all prescient stores are matched by an *Assign* such that e must be empty in the end. From  $e = \varepsilon$  we immediately get  $\Gamma' \sim \Delta'$ . Also from  $(\Delta, \varepsilon) \rightarrowtail^* (\Delta', \varepsilon)$  we can strip off a derivation  $\Delta \longrightarrow^* \Delta'$  by definition of  $\rightarrowtail$ .

The second claim follows just by transitivity of  $\sim$  as  $\Delta_1' \sim \Gamma' \sim \Delta_2'$ .

For our running example we can conclude that the corollary is applicable if all threads write o exclusively in synchronized blocks.

### 7 Conclusion

We have presented an event space semantics for multi-threaded Java with prescient stores. The informal statements in [3, §17.8] have been formalized and proven completely. In fact, the main motivation for this work was to understand what they meant. Correspondingly, we presented an operational semantics for prescient stores by just refining the axioms of the event space, leaving untouched the laws of the operational semantics. This demonstrates the flexibility of the event space approach.

Future work will include the extension of the treated language, e.g. wait and notify, exceptions, method calls, and the application of the semantics to correctness proofs of Java programs.

Acknowledgement: We used Paul Taylor's diagram.sty.

#### References

- Ken Arnold and James Gosling. The Java Programming Language. Addison-Wesley, Reading, Mass., 1996.

- Pietro Cenciarelli, Alexander Knapp, Bernhard Reus, and Martin Wirsing. From Sequential to Multi-Threaded Java: An Event-Based Operational Semantics. In Proc. 6<sup>th</sup> Int. Conf. Algebraic Methodology and Software Technology, Lect. Notes Comp. Sci., Berlin, 1997. Springer. To appear.

- James Gosling, Bill Joy, and Guy Steele. The Java Language Specification. Addison— Wesley, Reading, Mass., 1996.

- Doug Lea. Concurrent Programming in Java. Addison-Wesley, Reading, Mass., 1997.

- Gordon D. Plotkin. Structural Operational Semantics (Lecture notes). Technical Report DAIMI FN-19, Aarhus University, 1981 (repr. 1991).

- Glynn Winskel. An Introduction to Event Structures. In Jacobus W. de Bakker, editor, Linear Time, Branching Time and Partial Order in Logics and Models for Concurrency, volume 354 of Lect. Notes Comp. Sci., Berlin, 1988. Springer.