# Fault-tolerant Execution of Parallel Applications on x86 Multi-core Processors with Hardware Transactional Memory

Dissertation

zur Erlangung des akademischen Grades eines Doktors der Ingenieurwissenschaften (Dr.-Ing.) der Fakultät für Angewandte Informatik der Universität Augsburg

eingereicht von Florian Ludwig Haas, M. Sc.

# Fault-tolerant Execution of Parallel Applications on x86 Multi-core Processors with Hardware Transactional Memory

Florian Ludwig Haas, M. Sc.

| Erstgutachter:              | Prof. Dr. Theo Ungerer   |

|-----------------------------|--------------------------|

| Zweitgutachter:             | Prof. Dr. Bernhard Bauer |

| Tag der mündlichen Prüfung: | 22. Juli 2019            |

## Zusammenfassung

Um der anhaltenden Nachfrage nach zunehmender Rechenleistung gerecht zu werden, versuchen die Hersteller das Verhältnis von Rechenleistung zu verbrauchter elektrischer Leistung zu erhöhen, was durch Verkleinerung der Strukturgrößen elektronischer Schaltkreise erreicht werden kann. Jedoch werden die Grenzen des technologisch Machbaren bald erreicht sein, und eine weitere Absenkung der Versorgungsspannung sowie die Erhöhung der Taktraten führen zu steigenden Fehlerraten aufgrund transienter Fehler, die aus der Miniaturisierung der Transistoren und deren zunehmender Anzahl auf einem Chip resultieren.

Solchen Fehlern kann entgegen gewirkt werden, indem Techniken von hochverfügbaren Serversystemen, sowie aus sicherheitskritischen eingebetteten Systemen auch in Standardsysteme integriert werden. Die typische Lockstep-Ausführung, bei der die Zustände zweier redundanter Prozessoren taktweise verglichen werden, ist in komplexen out-of-order Prozessoren kaum umsetzbar. Es wurden jedoch Ansätze vorgestellt, die eine lose Kopplung ermöglichen, sowohl integriert in Hardware, als auch rein Software-basiert. Software-Ansätze ermöglichen eine anwendungsspezifische redundante Ausführung zur Fehlererkennung auf einem COTS- (commercial-off-the-shelf, seriengefertigten) Prozessor ohne weitere Hardware-Anpassungen.

In den vergangenen Jahren erhielt die Transaktionsspeichertechnik zunehmende Aufmerksamkeit in der Forschung zu fehlertoleranten Systemen. Deren Eigenschaft der Isolation und der integrierte Mechanismus zur Erstellung von Sicherungspunkten zur Wahrung der Atomarität brachte mehrere Ansätze zur Verwendung von Transaktionsspeicher für Fehlertoleranz hervor. Mit der Verfügbarkeit erster Hardware-Implementierungen, zum Beispiel TSX in den teureren x86-Prozessoren der *Core*-Familie von Intel, wurden Software-Mechanismen möglich, die auf Hardware-Transaktionsspeicher basieren und dessen Rückrollfähigkeit für den Fehlerfall ausnutzen.

In dieser Dissertation wird eine fehlertolerierende Ausführung mit Transaktionsspeicher auf einem Intel-Prozessor untersucht, die auf lose gekoppelter redundanter Ausführung basiert. Ein Instrumentierungsverfahren, das als Optimierungsmodul für die LLVM-Compiler-Toolchain entwickelt wurde, und eine zu POSIX-Systemen kompatible Bibliothek stellen die Mechanismen für Fehlererkennung und Fehlerbehebung zur Verfügung. Funktionalität und Leistungsfähigkeit des Ansatzes wurden mit Benchmarks aus der SPEC2017-Benchmark-Suite getestet. Die Ergebnisse zeigen, dass eine fehlertolerante redundante Ausführung auf einem x86-Prozessor möglich ist, und dass spezifische Erweiterungen der Hardware die Leistungsfähigkeit noch weiter steigern können.

Die redundante Ausführung mehrfädiger Anwendungen erfordert eine besondere Betrachtung, da indeterministisches Verhalten aufgrund auseinanderlaufender Synchronisierung zwischen redundanten Paaren von Threads auftreten kann, zum Beispiel bei gegenseitigem Ausschluss. Es wird eine Schnittstelle zu den Pthread-Synchronisierungsfunktionen und ein Mechanismus zur Fehlerbehebung beschrieben, um die redundante und fehlertolerierende Ausführung mehrfädiger Anwendungen zu ermöglichen. Dies wurde mithilfe von Benchmarks aus der PARSEC-Suite evaluiert, die die Machbarkeit redundanter Mehrfädigkeit auf COTS-Prozessoren zeigen und die nur geringe Auswirkung der zusätzlichen Schicht auf Leistungsfähigkeit und Skalierung bestätigen.

# Abstract

To satisfy the enduring demand for increasing computational power, the processor manufacturers try to raise the performance per Watt of a chip, which can be achieved by minimizing the structure sizes of electronic circuits. However, the technological limits are about to be reached, and the further reduction of the supply voltages and rising frequencies will lead to increased error rates due to transient faults, which result from the miniaturization of transistors, and from the growing number of transistors on a chip.

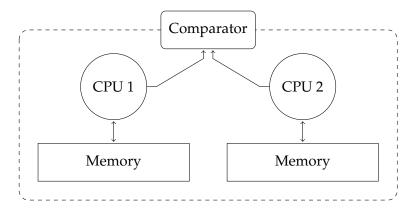

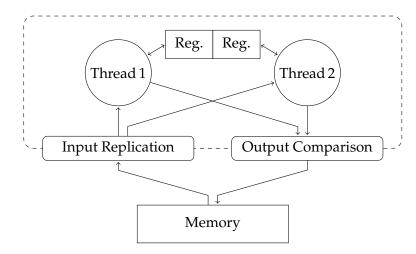

To mitigate such errors, techniques from dependable server systems and safety-critical embedded systems become attractive in commodity systems as well. However, the typically used cycle-by-cycle lockstep execution of a redundant processor is hardly feasible on a complex out-of-order CPU. Approaches that enable a loose coupling have been proposed, integrated in hardware as well as software-only approaches. Software mechanisms allow to run specific applications redundantly to detect errors on a COTS (commercial-off-the-shelf) processor without hardware modifications.

In recent years, transactional memory gained interest in the research of fault-tolerant systems. Its property of isolation and the integrated checkpointing mechanism to guarantee atomicity spawned multiple approaches to utilize transactional memory for fault tolerance. With the availability of first hardware implementations, for example TSX in the more expensive processors of the Intel x86 *Core* family, software mechanisms that rely on hardware transactional for checkpointing became feasible.

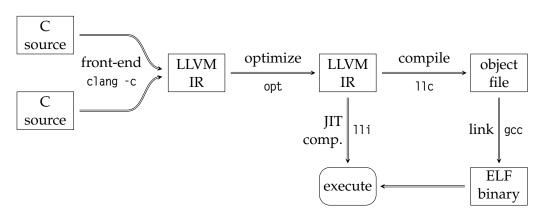

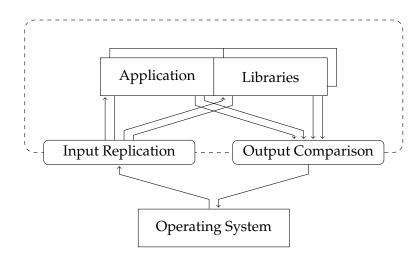

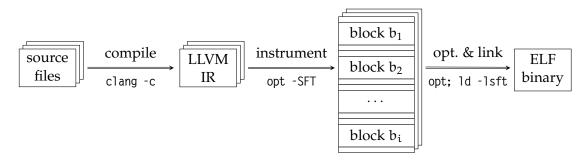

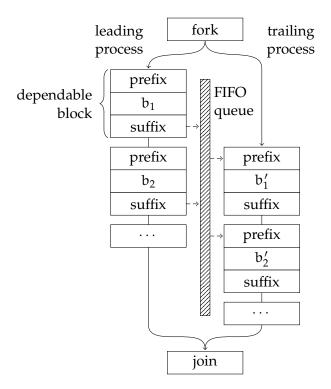

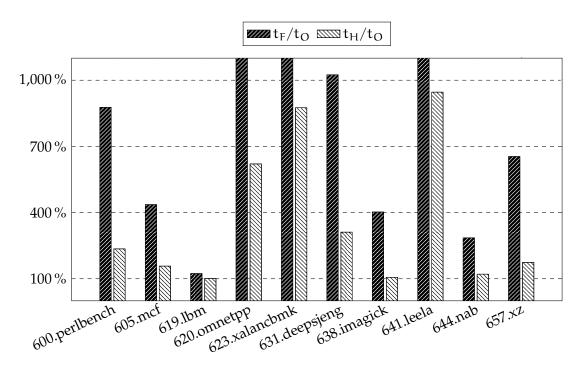

This thesis investigates a fail-operational execution with transactional memory on a COTS Intel CPU, based on loosely-coupled redundant execution. An instrumentation mechanism, which was developed as an optimization pass for the LLVM compilation toolchain, and a support library for POSIX compatible systems provide the functionality for error detection and recovery. The feasibility and the effectiveness of the approach were evaluated with benchmarks of the SPEC2017 benchmark suite. Results show that a fault-tolerant redundant execution can be achieved on an x86 CPU, and that specific enhancements to the hardware could further improve the overall performance.

Multi-threaded applications require further consideration for redundant execution, since indeterminism can occur between redundant pairs of threads, due to diverging synchronization, for example on mutual exclusion. An interface to the Pthread synchronization functions is described, as well as an error recovery mechanism, to enable the redundant and fail-operational execution of multi-threaded applications. This was evaluated by means of benchmarks of the PARSEC suite to prove that redundant multi-threading is feasible on a COTS CPU. The impact of the additional layer on performance and speedup is shown to be minimal.

# Danksagung

Großer Dank gilt meinem Doktorvater, Prof. Dr. Theo Ungerer, für die Unterstützung beim Verfassen der Dissertation durch kritische und konstruktive Ratschläge. Teil seines Lehrstuhls zu sein, sowie im Rahmen eines Drittmittelprojekts internationale Kontakte mit Forschern zu knüpfen, trugen wesentlich zur Themenfindung und Konzeptentwicklung dieser Arbeit bei. Ebenfalls bedanken möchte ich mich bei Herrn Prof. Dr. Bernhard Bauer für die Begutachtung dieser Arbeit.

Meinen Kollegen am Lehrstuhl für Systemnahe Informatik und Kommunikationssysteme an der Universität Augsburg danke ich für die unzähligen, die eigene Kreativität fördernden Diskussionen fachlicher und privater Natur. Dr. habil. Florian Kluge und Dr. Stefan Metzlaff sei ganz besonders gedankt, da durch sie der Kontakt zum Lehrstuhl während meines Studiums entstand, und durch deren Betreuung in Vorlesungen, Praktika und in der Masterarbeit mein Interesse in diesem Fachgebiet geweckt wurde, was letztlich zur Arbeit an dem dieser Dissertation zugrunde liegenden Forschungsprojekt führte. Bei Dr. Sebastian Weis bedanke ich mich für die jahrelange und freundschaftliche Zusammenarbeit bei Forschungsprojekten und in der Lehre, sowie für die zahlreichen Diskussionen, die einen wesentlichen Beitrag zu dieser Arbeit geleistet haben.

Meiner Familie und besonders meiner Ehefrau Sonja möchte ich für ihre Geduld und die andauernde Unterstützung danken, die mir das Verfassen dieser Arbeit erst ermöglicht haben.

Florian Haas Augsburg im Juli 2019

# Contents

| <ol> <li>1.1</li> <li>1.2</li> <li>1.3</li> </ol> |            |                                                                                                                | <b>13</b><br>14<br>15<br>16 |

|---------------------------------------------------|------------|----------------------------------------------------------------------------------------------------------------|-----------------------------|

| 2 I                                               | Background | I de la construcción de la constru | 17                          |

| 2.1                                               | Fault Tole | rance                                                                                                          | 18                          |

|                                                   | 2.1.1      | From Fault to Failure                                                                                          | 18                          |

|                                                   | 2.1.2      | Fault Duration                                                                                                 | 20                          |

|                                                   | 2.1.3      | Effects of Technology Scaling on Fault Rates                                                                   | 22                          |

|                                                   | 2.1.4      | Error Models                                                                                                   | 22                          |

|                                                   | 2.1.5      | Redundancy                                                                                                     | 23                          |

|                                                   | 2.1.6      | Error Detection with Lockstep Execution                                                                        | 26                          |

|                                                   | 2.1.7      | Loosely-coupled Redundant Execution                                                                            | 27                          |

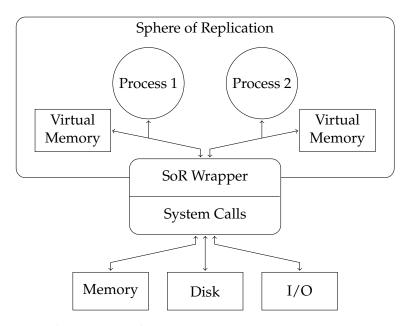

|                                                   | 2.1.8      | Sphere of Replication                                                                                          | 28                          |

| 2.2                                               | Multi-Th   | reading in Shared-Memory Systems                                                                               | 30                          |

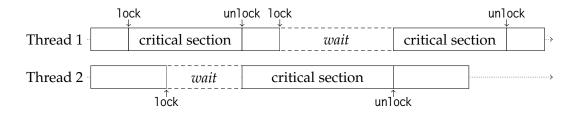

|                                                   | 2.2.1      | Synchronization with Mutual Exclusion                                                                          | 30                          |

|                                                   | 2.2.2      | Lock-free Data Structures                                                                                      | 31                          |

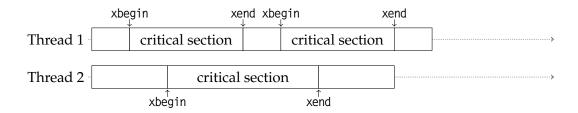

| 2.3                                               | Hardware   | e Transactional Memory                                                                                         | 32                          |

|                                                   | 2.3.1      | Version Management                                                                                             | 33                          |

|                                                   | 2.3.2      | Conflict Detection and Resolution                                                                              | 33                          |

|                                                   | 2.3.3      | Intel Transactional Synchronization Extensions                                                                 | 34                          |

| 2.4                                               | Software   | Fault Tolerance with Hardware Support for Error Detection and                                                  |                             |

|                                                   | Recovery   |                                                                                                                | 37                          |

|                                                   | 2.4.1      | Transactional Memory in Dependable Systems                                                                     | 38                          |

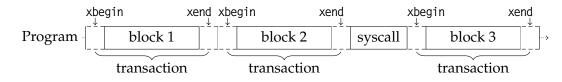

|                                                   | 2.4.2      | Transaction Checkpoints for Error Recovery                                                                     | 38                          |

| 2.5                                               | The LLVN   | A Compilation Framework                                                                                        | 39                          |

|                                                   | 2.5.1      | LLVM Intermediate Representation                                                                               | 40                          |

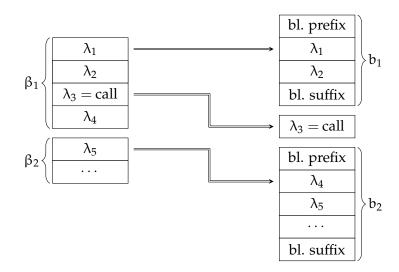

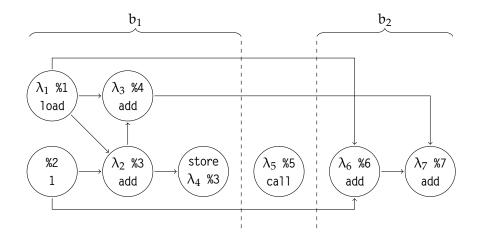

|                                                   | 2.5.2      | Program Instrumentation with an LLVM Optimization Pass                                                         | 42                          |

| 2.6                                               | Summary    | · · · · · · · · · · · · · · · · · · ·                                                                          | 42                          |

| <b>.</b>                                          |            |                                                                                                                | 4 -                         |

|                                                   | Related Wo |                                                                                                                | 45                          |

| 3.1                                               | Hardware   | e Redundancy Approaches                                                                                        | 46                          |

|                                                   |            |                                                                                                                |                             |

|     | 3.1.1                                                                                                                                                                    | NonStop Advanced Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 46                                                                                           |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

|     | 3.1.2                                                                                                                                                                    | Simultaneous and Redundantly Threaded Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 46                                                                                           |

|     | 3.1.3                                                                                                                                                                    | Dynamic Core Coupling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 47                                                                                           |

| 3.2 |                                                                                                                                                                          | based Redundancy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 48                                                                                           |

|     | 3.2.1                                                                                                                                                                    | Error Detection by Duplicated Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 48                                                                                           |

|     | 3.2.2                                                                                                                                                                    | Software Implemented Fault Tolerance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 49                                                                                           |

|     | 3.2.3                                                                                                                                                                    | Software-based Redundant Multi-threading                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 49                                                                                           |

|     | 3.2.4                                                                                                                                                                    | Process-Level Redundancy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 50                                                                                           |

| 3.3 | Transactio                                                                                                                                                               | onal Memory for Fault Tolerance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 51                                                                                           |

|     | 3.3.1                                                                                                                                                                    | FaulTM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 51                                                                                           |

|     | 3.3.2                                                                                                                                                                    | Log-based Redundant Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 52                                                                                           |

|     | 3.3.3                                                                                                                                                                    | Hardware-Assisted Fault Tolerance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 52                                                                                           |

| 3.4 | Redunda                                                                                                                                                                  | nt Execution of Multi-threaded Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 53                                                                                           |

|     | 3.4.1                                                                                                                                                                    | RomainMT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 53                                                                                           |

|     | 3.4.2                                                                                                                                                                    | FaulTM-multi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 53                                                                                           |

|     | 3.4.3                                                                                                                                                                    | Redundant Execution of OpenMP and Message-passing Programs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 54                                                                                           |

| 3.5 | Comparis                                                                                                                                                                 | son of the Related Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 55                                                                                           |

| 3.6 | Summary                                                                                                                                                                  | <i>,</i> ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 57                                                                                           |

|     |                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -0                                                                                           |

|     |                                                                                                                                                                          | Execution of Single-Threaded Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>59</b>                                                                                    |

|     |                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                              |

| 4.1 |                                                                                                                                                                          | Hardware/Software Approach for Fault-Tolerance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 60                                                                                           |

| 4.1 | 4.1.1                                                                                                                                                                    | Target Platform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 60                                                                                           |

| 4.1 | 4.1.1<br>4.1.2                                                                                                                                                           | Target Platform    Transactional Execution for Error Containment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 60<br>61                                                                                     |

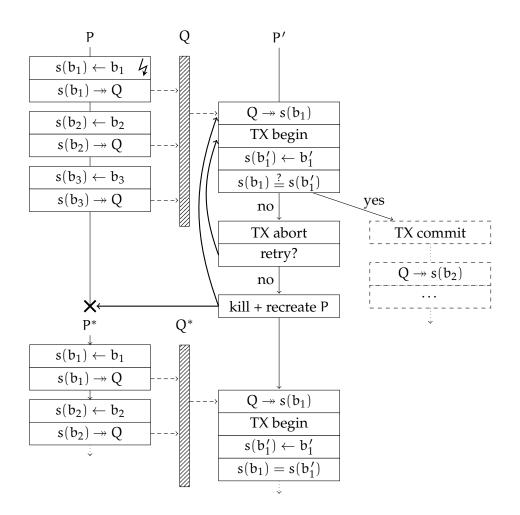

| 4.1 | 4.1.1<br>4.1.2<br>4.1.3                                                                                                                                                  | Target PlatformTransactional Execution for Error ContainmentError Detection and Recovery with Loosely-Coupled Redundancy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 60<br>61<br>61                                                                               |

|     | 4.1.1<br>4.1.2<br>4.1.3<br>4.1.4                                                                                                                                         | Target PlatformTransactional Execution for Error ContainmentError Detection and Recovery with Loosely-Coupled RedundancyError Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 60<br>61<br>61<br>63                                                                         |

| 4.1 | 4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>Instrume                                                                                                                             | Target Platform       Target Platform         Transactional Execution for Error Containment       Error Detection and Recovery with Loosely-Coupled Redundancy         Error Model       Error Model         Intation       Intation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 60<br>61<br>61<br>63<br>63                                                                   |

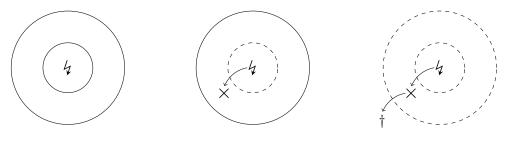

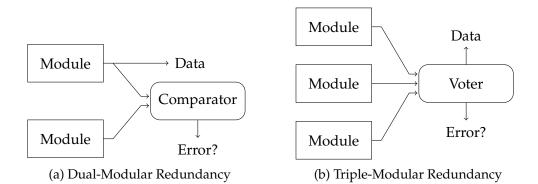

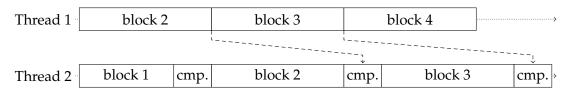

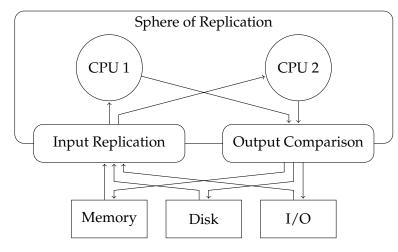

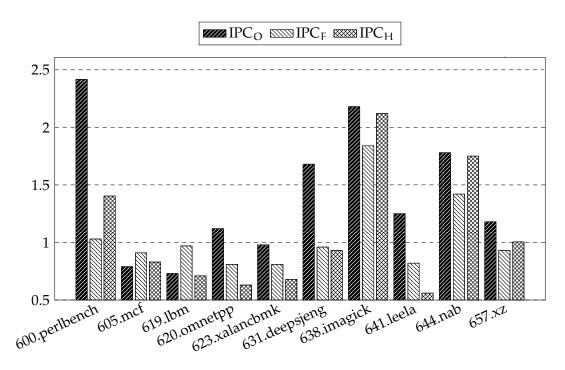

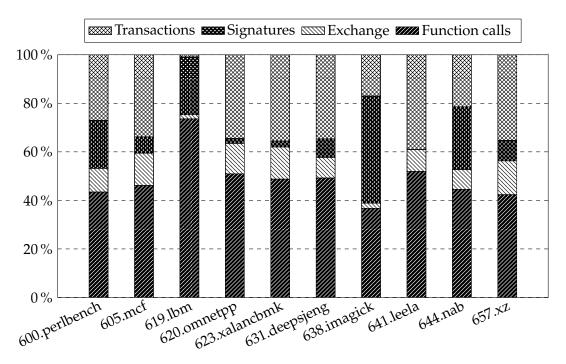

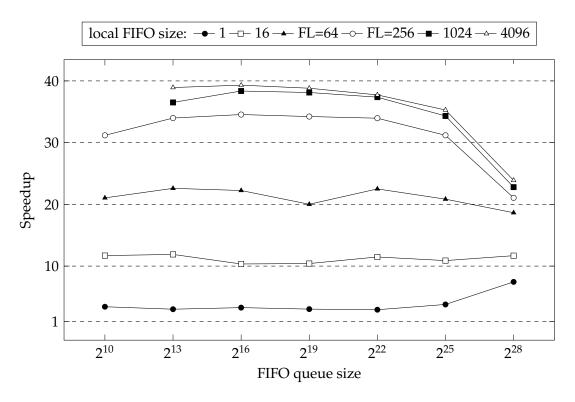

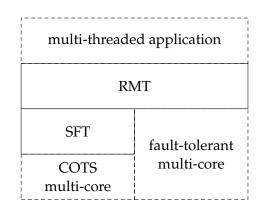

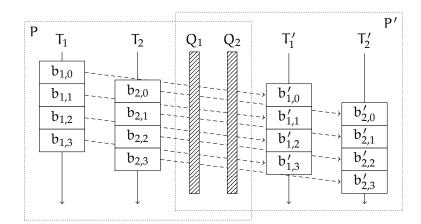

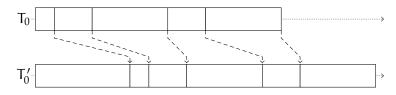

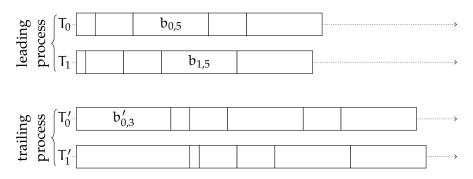

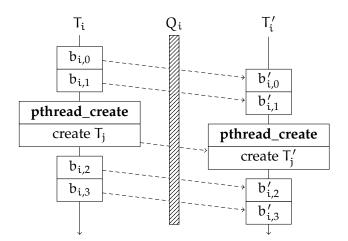

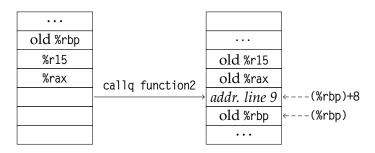

|     | 4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>Instrume<br>4.2.1                                                                                                                    | Target Platform       Transactional Execution for Error Containment         Tror Detection and Recovery with Loosely-Coupled Redundancy         Error Model         ntation         Functions and Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 60<br>61<br>63<br>63<br>63                                                                   |