# A Survey of Timing Verification Techniques for Multi-Core Real-Time Systems

CLAIRE MAIZA and HAMZA RIHANI, Université Grenoble Alpes, CNRS, Grenoble INP,

VERIMAG, France

JUAN M. RIVAS and JOËL GOOSSENS, Université libre de Bruxelles, PARTS

Research Centre, Belgium

SEBASTIAN ALTMEYER, University of Amsterdam, Netherlands

ROBERT I. DAVIS, University of York, UK

This survey provides an overview of the scientific literature on timing verification techniques for multi-core real-time systems. It reviews the key results in the field from its origins around 2006 to the latest research published up to the end of 2018. The survey highlights the key issues involved in providing guarantees of timing correctness for multi-core systems. A detailed review is provided covering four main categories: full integration, temporal isolation, integrating interference effects into schedulability analysis, and mapping and allocation. The survey concludes with a discussion of the advantages and disadvantages of these different approaches, identifying open issues, key challenges, and possible directions for future research.

CCS Concepts: • Computer systems organization  $\rightarrow$  Real-time system architecture; • Software and its engineering  $\rightarrow$  Real-time schedulability; Automated static analysis;

Additional Key Words and Phrases: Real-time systems, architecture, multi-core, timing analysis, schedulability analysis, WCET, co-runner interference

## **ACM Reference format:**

Claire Maiza, Hamza Rihani, Juan M. Rivas, Joël Goossens, Sebastian Altmeyer, and Robert I. Davis. 2019. A Survey of Timing Verification Techniques for Multi-Core Real-Time Systems. *ACM Comput. Surv.* 52, 3, Article 56 (June 2019), 38 pages.

https://doi.org/10.1145/3323212

#### 1 INTRODUCTION

Multi-core processors offer significantly higher computing performance, as well as advantages in meeting SWaP (Size, Weight, and Power consumption) requirements compared to conventional single-core platforms. Such architectures have the potential to provide a solution to the increasing

The research that went into writing this paper was funded in part by the ESPRC grant MCCps (EP/P003664/1), the Innovate UK grant SECT-AIR (113099), and by the Wallonia Region (Belgium) BEWARE grant PARTITA (1610375). EPSRC Research Data Management: No new primary data was created during this study.

Authors' addresses: C. Maiza and H. Rihani, Verimag, 700 avenue centrale, bâtiment IMAG, 38402, Saint Martin d'Hères, France; email: claire.maiza@univ-grenoble-alpes.fr; J. M. Rivas and J. Goossens, Université libre de Bruxelles CP 212, 50 avenue F. D. Roosevelt, 1050 Brussels, Belgium; email: joel.goossens@ulb.ac.be; S. Altmeyer, Informatics Institute, Postbus 94323, 1090 GH Amsterdam; email: altmeyer@uva.nl; R. I. Davis, Department of Computer Science, University of York, Deramore Lane, York, YO10 5GH, UK; email: rob.davis@cs.york.ac.uk.

© 2019 Copyright held by the owner/author(s). Publication rights licensed to ACM. This is the author's version of the work. It is posted here for your personal use. Not for redistribution. The definitive Version of Record was published at https://doi.org/10.1145/3323212

demands for low-cost, low-power consumption, high-performance real-time hardware platforms that are posed by the development of autonomous systems, including self-driving cars, Unmanned Aerial Vehicles (UAVs) or drones, and autonomous robots. While providing a number of significant advantages, the shift to multi-core hardware raises substantial challenges in relation to guaranteeing real-time performance through time determinism, time predictability, and composability.

Real-time systems are characterised by the need to meet both functional requirements and timing constraints, typically expressed in terms of deadlines. Many design and verification techniques have been proposed which aim to guarantee that all timing constraints are met. In traditional single-core systems, timing behaviour is typically verified via a two-step process. In the first timing analysis step, the Worst-Case Execution Time (WCET) of each task is determined. The WCET is an upper bound on the execution time of the task running in full isolation on the platform, i.e., without preemption, interruption, or indeed any co-runners on other processing cores. This WCET bound is then used in the second step, schedulability analysis. Schedulability analysis involves considering the worst-case pattern of task execution, either via the mapping of tasks to time slots in a table-driven schedule, or via the use of a scheduling policy such as Fixed-Priority Preemptive Scheduling (FPPS) or Earliest Deadline First (EDF) employed by a Real-Time Operating System (RTOS). Schedulability analysis determines the Worst-Case Response Time (WCRT) of each task in its execution context. In practice, this analysis needs to take account of preemptions by higher priority tasks and interrupt handlers, scheduling overheads caused by the operation of the RTOS, and delays in accessing shared software resources and communications. The combination of timing analysis and schedulability analysis to verify the timing correctness of a real-time system is referred to in this survey as timing verification.<sup>1</sup>

The clear separation between the two steps diminishes in multi-core systems where the interference on shared resources can also depend heavily on the behaviour of co-runners, i.e., tasks executing in parallel on other cores. In multi-core platforms a large set of hardware features may be shared, such as the interconnect, bus<sup>2</sup> or NoC (Network on Chip), the Last Level Cache (LLC), and the main memory. When a task is executed in full isolation on a multi-core platform, the behaviour of the system in terms of timing (and other non-functional properties such as power consumption) is defined by that task alone, the same as on a single-core platform. However, when two or more tasks are executed in parallel on different cores the interplay between the tasks on shared hardware resources may lead to unforeseen and unpredictable delays [32, 123, 124]. For this reason, using the WCET of tasks executing in isolation on a multi-core platform, without regard for co-runner interference, can potentially lead to WCRT values that are *optimistic* (i.e., incorrect) by a large margin when considered in the context of the complete system. As an example, consider a cache that is shared between two or more cores. Useful cache blocks that were loaded by one task may be evicted by another task that is running in parallel on a different core. Similarly, a request to the memory bus may be blocked by an ongoing bus request from another core. We refer to all events that may prolong a task's execution due to the execution of other tasks, including additional blocking time, increased bus access times, and cache reloads, under the generic term interference. The potential for co-runner interference greatly exacerbates both the difficulty and the complexity of providing accurate timing verification for multi-core systems. To illustrate this, consider the simple approach of accounting for all possible co-runner interference in the timing analysis step. The difficulty here is that the execution context, with respect to co-runner behaviour, is unknown. Thus, worst-case assumptions need to be made to provide a WCET that is context independent.

<sup>&</sup>lt;sup>1</sup>We note that in some of the literature the term *timing analysis* is used to describe the overall process of determining whether timing constraints are met.

<sup>&</sup>lt;sup>2</sup>In this article, as in many of the surveyed papers, we use the term *bus* or *memory bus* to mean a local interconnect from cores to the shared memory through an arbiter.

This is possible, however, the results can be so pessimistic that they are not useful. For example, assuming the maximum possible delay for every bus access request may result in a WCET on an m core platform that is m or more times the WCET for the task running in isolation. Thus, the guaranteed real-time performance of the multi-core platform is effectively degraded to the same or worse than that of one of its cores.

At the other extreme, attempting to account for all possible patterns and interleaving of corunner execution in a fully integrated approach to timing verification (combining both execution and scheduling considerations into a single analysis step) quickly becomes intractable due to a combinatorial explosion in the number of possible states that need to be considered. Hence, timing verification for multi-core systems typically faces the tradeoff between analysing all possible interplay between tasks on different cores to provide a tightly bounded result, and making simplifying assumptions to obtain an analysis that is tractable in terms of its computational complexity.

A number of approaches have been proposed to deal with this problem. Approaches based on *temporal isolation* seek to bound the delays experienced by tasks executing on one core, independent of the behaviour of the tasks on the other cores. For example, using Time Division Multiple Access (TDMA) bus arbitration leads to the same delays for bus access requests irrespective of whether or not there are any tasks running on the other cores. While this is advantageous in terms of making it simpler to compute worst-case delays and interference, there is a tradeoff. Mechanisms that provide temporal isolation have the disadvantage that they typically do not permit efficient resource utilisation.

Techniques that ensure temporal isolation between cores provide *timing composability*, meaning that the timing behaviour of the tasks on one core can be verified without knowledge of the behaviour of the tasks on the other cores. An alternative approach is *interference analysis*, characterising the additional delays due to contention over shared resources. These additional delays can then be incorporated into timing analysis or schedulability analysis. Examples of interference analysis in single-core systems include the derivation of cache-related preemption delays and write-back delays, which can be incorporated into schedulability analysis.

Another challenge that timing verification for multi-core systems has to tackle is the problem of *timing compositionality* [53] (note this is different from timing composability). Timing compositionality depends on the decomposition of the system into components for analysis purposes. For example, the WCET of a task might be decomposed into two components, memory access time and processing time. If the local worst-cases for each component of the decomposition can be summed to obtain an upper bound on the overall worst-case timing behaviour, then the decomposition is said to be *timing compositional*. However, in multi-core systems this is not always the case. Timing anomalies, such as the interaction between caches and pipelines, can mean that a local worst-case behaviour, e.g., a cache miss, may not always lead to the overall worst-case. Further, domino effects [53] can amplify and reinforce the effects of interference. For example, preemption effects on a First-In First-Out (FIFO) cache can cause additional delays that are effectively unbounded with respect to the original perturbation.

Research on timing verification for multi-core systems has received increasing attention over the past 10 years, with a number of often orthogonal and sometimes incompatible approaches introduced. In this survey, we provide an overview of the main approaches proposed and a review of the specific methods published in the literature.

#### 1.1 Organisation

Research into timing verification of multi-core real-time systems can be classified into four main categories. This classification forms the basis for the four main sections of this survey. For ease of reference, we have numbered these categories below to match the section numbering, starting at 2.

- 2 Full Integration: Research in this category considers full information about the behaviour of the various tasks executing on the different cores, including when they can execute and their individual resource demands. The detailed interference due to specific co-runners executing within specific time intervals is thus integrated into the analysis for every task. The timing analyses in this category are therefore context-dependent (i.e., the results for each task depend on the set of co-runners).

- 3 *Temporal Isolation*: Research in this category considers either partial or full temporal isolation achieved via software means such as phased task execution, memory bus regulation, or static offline scheduling; or via hardware means such as a TDMA bus arbitration and memory partitioning. The aim being to either upper bound or eliminate the interference from co-runners that needs to be considered in the analysis. The timing analyses reviewed in this category are therefore context-independent (i.e., the results for each task are independent of the actual set of co-runners).

- 4 *Integrating Interference Effects into Schedulability Analysis*: Research in this category integrates the effects of co-runner interference and the use of shared hardware resources into schedulability analysis. In this case, the analysis may take into account the behaviour of the actual co-runners, or it may rely on worst-case assumptions that are valid for any co-runner. Thus, both context-dependent and context-independent analyses are possible. For example, both are possible when considering a bus with Round-Robin arbitration.

- 5 *Mapping and Scheduling*: Research in this category considers the mapping of tasks to cores and their feasibility in terms of both timing behaviour and memory requirements. Here, the processor and memory load on each core, as well as the impact of interference delays, influence the optimal placement of tasks.

Each of the main Sections 2–5 starts with an overview and ends with a critique and perspectives on the research in that specific area. A few papers overlap this broad categorisation. In these cases, we provide a review in one section and a cross-reference to it in the other. Section 6 discusses the main advantages and disadvantages of techniques in the four main categories. It concludes with an identification of key open questions and important directions for future research. Supplementary material in Appendix A provides a more detailed classification of the literature according to various characteristics and properties relating to: (i) the type of timing verification performed; (ii) the timing model used for the analysis; (iii) the hardware properties considered; and (iv) the software properties considered.

Note, due to space limitations, we do not provide an overview of embedded multi-core architectures and hardware components; rather, we assume that the reader has a basic working knowledge of these topics (see [111] for a state-of-the-art in the context of time-predictable embedded multi-core architectures, and [115] for a discussion of more advanced Commercial-Off-The-Shelf (COTS) multi-cores).

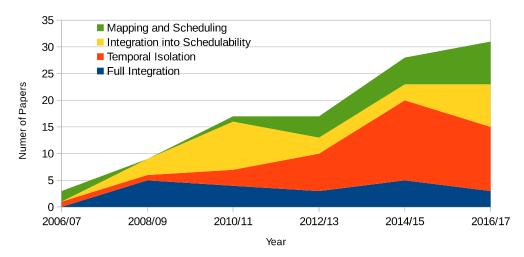

It is interesting to note how research in the different categories has progressed over time. Figure 1 illustrates the number of publications in each of the four main categories in each 2-year period from 2006/7 to 2016/17. (This figure is best viewed online in colour). A number of observations can be drawn from Figure 1. Firstly, the research topic is little more than a decade old. Of the 119 papers reviewed,<sup>3</sup> the oldest papers [7, 120] that we classified were published in 2006. Since 2006, the research intensity in this area has increased rapidly, with around 60% of the papers published in the last 4 years. We can also observe trends with respect to the approach taken to timing verification. Although the number of publications aiming for a fully integrated timing and schedulability analysis (see Section 2) remained largely constant over the past 10 years, all

<sup>&</sup>lt;sup>3</sup>Note, not all of the bibliography is classified papers, some are related work.

Fig. 1. Distribution of classified papers over the past 10 years.

other categories have received increasing attention. In particular, the vast majority of the papers on temporal isolation (Section 3) and on mapping and scheduling (Section 5) have been published in the last 6 years.

We note that the literature covers a large number of separate research threads (within which papers build on the same model and assumptions); however, these various threads of research are highly divergent with the different hardware and task models used meaning that sophisticated comparisons between different analysis results are out of reach.

#### 1.2 Related Areas of Research and Restrictions on Scope

The scope of this survey is restricted to timing verification techniques for multi-core and manycore platforms that specifically consider the impact of shared hardware resources. The following areas of related research are outside of the scope of this survey: (i) works that introduce isolation mechanisms for multi-core systems, but rely on existing analysis for timing verification (examples include the work on the MERASA [94] and T-CREST projects [111]), as well as work on shared cache management techniques (surveyed in [46]) and cache coherence [47, 56]; (ii) works that introduce mechanisms and analyses of the worst-case latencies for a particular component, for example, predictable DDR-DRAM memory controllers<sup>4</sup> (comparative studies in [49, 57]), but rely on these latencies being incorporated into existing analyses for timing verification; (iii) scheduling and schedulability analyses for multiprocessor systems that consider only a simple abstract model of task execution times (surveyed in [38]); (iv) multiprocessor software resource sharing protocols; (v) timing verification techniques for many-core systems with a NoC (surveyed in [59, 70]) that consider only the scheduling of the NoC, or consider that tasks on each core execute out of local memory with the only interaction with packet flows being through a consideration of release jitter; (vi) measurement-based timing analysis and measurement-based probabilistic timing analysis; and (vii) research that focuses on timing verification of single-core systems. Further, the survey does not cover specific research into multi-cores with GPGPUs or re-configurable hardware.

#### 2 FULL INTEGRATION

Research in this category aims at a fully integrated analysis utilising information about both low-level timing behaviour and high-level scheduling. Thus, the works discussed in this section

<sup>&</sup>lt;sup>4</sup>We note that Reduced Latency DRAM (RL-DRAM) is arguably better suited for use in real-time systems than DDR-DRAM, due to reduced variability in access latencies, as shown by Hassan [55] in 2018.

assume almost *full knowledge* of the task under analysis and those executed in parallel, often including the exact release times of all tasks. Consequently, the results are typically only valid for the *exact scenario* that is analysed. Two approaches are dominant: WCET analyses based on *model-checking* and analyses based on an *abstract processor state*. The worst-case path (i.e., the path with the longest execution time) is often derived via Implicit-Path Enumeration Techniques (IPET) with an Integer Linear Programming (ILP) solver. We note that all of the works assume partitioned non-preemptive scheduling. Further, the schedule is often assumed to be fixed with synchronous task releases and limited or no release jitter. Below, we subdivide the literature into analyses that focus on (i) shared memory (i.e., cache), (iii) the bus or interconnect, and (iii) both the interconnect and shared memory.

## 2.1 Analysis of Shared Memory Only

Papers in this sub-category focus solely on the shared cache, while neglecting any interference on the common interconnect. Cache analyses either employ a complete model of the cache state, and thus use model checking to derive a cache hit/miss classification, or they employ an abstract cache state with a variant of abstract interpretation.

In 2008, Yan and Zhang [128] presented a cache analysis assuming private L1 and shared L2 caches. The analysis starts with a cache analysis assuming no interference, and then accounts for the additional L2 cache misses due to accesses from other tasks to the L2 cache. The analysis is implemented within CHRONOS and evaluated for direct-mapped instruction caches only. In 2009, Hardy et al. [54] extended this initial work to set-associative caches, multiple levels of caches, and an arbitrary number of competing cores. A further extension aims to reduce the cache interference via compiler optimisations that classify memory as reused and therefore cached, or not-reused, in which case accesses bypass the cache. Zhang and Yan [137] also presented an interference analysis for shared L2 instruction caches. They use an extended ILP and cache conflict graphs to model all possible interleaving of pairs of tasks with regard to cache accesses. These interleavings are more precisely defined than in [128], but this results in a scalability issue.

A WCET analysis based on *model checking* was presented by Gustavsson et al. [51] in 2010. The modelled architecture again features private L1 caches, shared L2 caches, and a set of tasks, but no explicitly modelled interconnect. Instead, the authors assume dedicated memory ports per core. The core architecture is assumed to be trivial with fixed execution times per instruction and without any timing anomalies. UPPAAL is used as the model checker and, despite the strong simplifications, the state-space explosion limits the applicability of the approach, even without modelling the program semantics.

Also in 2010, Lv et al. [82] combined abstract interpretation and model checking to provide a fully integrated analysis. Abstract interpretation is used to give a basic block timing model. Timed automata are then used to model the whole program and the shared bus. The authors consider a multi-core architecture with a local L1 cache and no code sharing between concurrent programs. Each L1 cache miss is considered as a shared bus access. The analysed shared bus arbiters are First-Come First-Served (FCFS) and TDMA, with the approach scaling better in the case of TDMA due to the timing isolation provided. UPPAAL is the model checker used in the experiments.

In 2016, Nagar and Srikant [86] presented a shared cache analysis with private L1 and shared L2 caches. The analysis determines the global worst-case arrival pattern for all accesses to the shared cache including the worst-case execution path. The analysis is therefore independent from the precise task release times, but still requires precise knowledge about all tasks executing on the other cores. The authors show that finding the worst-case interference pattern is NP-hard and thus, as well as the exact analysis, an approximation with linear complexity in the cache size is proposed. The analysis is implemented within the CHRONOS timing analyser.

#### 2.2 Analysis of the Interconnect Only

Papers in this sub-category focus solely on the common interconnect. Interference due to shared memory is either ignored or full isolation is assumed. In all papers, the delay due to the interconnect is precisely estimated and integrated into the worst-case execution time.

In 2010, Andersson et al. [8] presented an analytical method to calculate the WCET of tasks on a multi-core including contention on the shared bus. They assume no inter-task evictions (i.e., the shared cache is partitioned) and non-preemptive scheduling. Further, the memory arbitration is assumed to be work-conserving. The analysis formulation is based on an upper bound on the maximum number of bus requests from the tasks.

In 2015, Rihani et al. [103] used SAT Modulo Theory (SMT) to encode the whole execution of a task on a platform with TDMA bus arbitration. The novelty here is the encoding of the program semantics to gain precision in the WCET bound, taking infeasible execution paths into account. The bus access is modelled with an offset. The SMT-solver provides an execution path with correct semantics and WCET analysis.

In 2015, Jacobs et al. [62] proposed deriving WCET bounds for multi-core systems by integrating the bus delay into the pipeline analysis. The authors assume a shared bus policy with bounded blocking time (e.g., Round-Robin or TDMA). For a memory access over the shared bus, the entire range of possible blocking delays is considered, i.e., direct access to the bus, blocked for one cycle, two cycles, and so on. In the so-called co-runner insensitive analysis, this scheme is applied to all bus accesses made by the analysed task, and assuming the entire range of blocking cycles. In the co-runner sensitive analysis, information about potential accesses from other tasks is considered to reduce the over-approximation. This assumes precise knowledge about when memory accesses of co-running tasks can occur.

Subsequently, in 2016, Jacobs et al. [63] presented a framework for the derivation of WCET analyses for multi-core systems. They point out that computing the WCET taking into account all possible inter-leavings of resource accesses is computational intractable. They make the key point that the vast majority of work assumes timing compositionality, and hence first compute a basic bound without interference effects and then add an upper bound on direct interference effects. However, for real architectures that exhibit timing anomalies and domino effects, this is not sufficient. The key idea in the paper is to lift system properties to an abstract level, so that they can be applied to the abstract model of traces to identify sets of infeasible traces, thus making the analysis less pessimistic. The framework is instantiated and used to provide bounds for the Malardalen benchmarks for 2, 4, and 8-core platforms, with either local scratchpad or cache, and in-order or out-of-order execution.

Research that overlaps with this sub-category but is reviewed elsewhere in this survey includes the work of Dasari et al. [35, 36] and Kelter et al. [66–68] (see Section 3.4).

#### 2.3 Analysis of Shared Memory and Interconnect

Papers in this sub-category consider both the common interconnect and shared memory.

In 2008, Andrei et al. [10] presented a WCET analysis technique in conjunction with an algorithm to build a static (offline) schedule for the tasks and the TDMA bus in multi-core systems. The authors target a platform model where the cores have a private cache, and then through the shared bus can access another private memory and a global shared memory. Only the private memories are cached. Inter-core communications are handled via the global shared memory. Additional tasks are added to handle the copy and writes to the global shared memory (i.e., explicit communications). A task can also produce implicit communications when a cache miss occurs, and

the private memory must be accessed via the bus. The proposed technique iteratively constructs the schedule of tasks and incrementally defines the TDMA slot configuration, taking into account task execution time inflation due to bus accesses.

An approach for worst-case response time analysis of a multi-core system with private L1 cache and shared L2 cache was developed by Li et al. [78] in 2009. The aim is to compute the worst-case L2 cache interference between tasks running on the different cores accounting for their lifetimes, i.e., the time intervals in which the tasks can be active. The model used is a synchronous one, with a Message Sequence Chart describing the interaction and precedence relations between tasks. Tasks are assumed to be partitioned to cores and to run non-preemptively. The WCET includes the effects of interference on the L2 cache. An iterative process is used to calculate WCRTs, task lifetimes, and the amount of interference from overlapping execution due to tasks on the other cores.

In 2012, Dasari et al. [34] presented a method to estimate tight WCETs of tasks running on a multi-core system in which the bus arbitration is Round-Robin, and tasks are scheduled non-preemptively under an unspecified non-work-conserving policy. The work is divided into two parts. The first part presents an algorithm to compute an upper bound of the number of memory requests by a core in any time window, considering the interference from every task at the same time (instead of analysing tasks independently and then adding their contributions). The actual schedule of jobs is unknown, which adds pessimism to the computed worst-case ordering of jobs. A second contribution of the paper is to use the provided upper bound on the number of requests to enhance the classical WCET formula for systems with Round-Robin buses.

A full analysis from WCET to mapping with interference analysis was presented by Boniol et al. [17] in 2012. This work focuses on the implementation of synchronous applications on a multicore platform. The architecture consists of cores with local L1 and L2 cache, and a shared main memory with shared bus and DRAM controller. The timing analysis consists of a core and memory mapping/scheduling with slicing of the timing window. It takes into account the interference on the shared bus and memory controller. The interference analysis is based on timed automata. This paper also takes a holistic view on WCET and schedulability analysis, but differs from all other papers in this category in that it focuses on the schedulability analysis directly.

In two papers in 2012 [24] and 2014 [23], Chattopadhyay et al. presented a WCET analysis that includes interference on a shared Round-Robin bus and a shared L2 cache. The global analysis is based on an ILP formulation (execution graph) of each delay from the pipeline to the bus and cache interferences. The delays are expressed as an interval and combined through solving the ILP. The bus analysis uses an offset model introduced by Chattopadhyay et al. [26] together with the cache model. The earlier work [24] assumes a timing-anomaly-free architecture, whereas the later one [23] supports architectures with timing anomalies and more sophisticated cache architectures.

In 2014, Kelter and Marwedel [69] analysed the WCET of *parallel* tasks. They estimate the execution time with a known synchronisation of the task releases. From this release cycle, an execution graph is derived at a cycle level and the access to shared resource is evaluated depending on which task is requesting access at that time. It is an IPET-based analysis (ILP system of constraints). There are three arbitration schemes modelled as part of the bus analysis: TDMA, Round-Robin, and priority based. The platform under analysis is a multi-core based on an Arm7 pipeline with local cache or scratchpad, and a shared bus to access shared memory. The authors mention that analysis of 8 cores was not possible due to scalability issues.

In 2016, Perret et al. [101] studied various sources of interference on COTS many-core platforms (similar to the Kalray MPPA-256). A realistic analysis is presented regarding the sources of interference between applications on their memory access path. The analysis focuses on local banked Static Random Access Memory (SRAM), NoC, and global Double Data Rate Synchronous DRAM

(DDR-SDRAM). The authors quantify the potential pessimism implied by a context-independent "worst-case-everywhere" calculation (i.e., with no assumptions about the competitors for each shared resource). They then propose recommendations for building viable execution models (complying to certain rules) in order to ease tight timing analysis (an extended version of these recommendations is presented by the same authors in [102]).

#### 2.4 Critique and Perspectives

Only 20 papers fall into the category of full integration analysis, and interestingly, these papers were nearly all written by researchers from groups that focus on static timing analysis and have developed their own tools (e.g., OTAWA, Heptane, CHRONOS, aiT, WCC) in the past. The scheduling aspect on multi-core systems is largely ignored by these papers and instead the task schedule is assumed to be known, fixed, and non-preemptive. How the schedule can be determined without initially knowing the WCETs is not explained in any of these works. This leads to an implicit restriction: the exact schedule including the release times at which tasks start executing must be known or at least approximated a priori. Many approaches in this category make an even stronger assumption in that they assume precise release times [23, 51, 63, 69, 128]. Any variation in release times may therefore invalidate the results. Consequently, these approaches can only be used if either (i) the operating system enforces the scenarios as analysed, or (ii) the analysis is repeated for all potential execution scenarios. In the first case, the system utilisation may be heavily reduced and it may even be infeasible to enforce the precise scenarios analysed, especially on large multicore systems with asynchronous clocks. In the second case, the number of scenarios that must be analysed is prohibitively large, even for small task sets. This problem adds to the fundamental drawback of these approaches: The fully integrated approaches suffer from high complexity and thus low scalability. This is particularly the case for approaches based on model-checking, but also affects those based on implicit path enumeration. The problem exists considering strongly simplified processor models that only model memory or the interconnect; modelling both types of components, let alone realistic multi-core architectures, further exacerbates the computational complexity. It is debatable whether any of these approaches can be used to analyse realistically sized task sets on non-trivial (i.e., realistic) multi-core architectures.

The need for full system knowledge also forecloses, or at least greatly complicates, common and desirable design practices such as integration of third party software and incremental verification.

#### 3 TEMPORAL ISOLATION

Research in this category simplifies the problem of multi-core timing verification by shaping access to the main sources of inter-core interference, mainly the shared interconnect or memory bus. The basic idea is that by controlling access to the memory bus, contention can be avoided or bounded, and thus becomes more predictable and easier to integrate into a timing analysis formulation. The result is analyses that are not only easier to define, but are also less computationally demanding and thus more scalable, particularly when compared to the full integration approaches reviewed in the previous section. The research work in this area identifies the *memory bus as the main source of inter-core interference* that must be controlled, and relies on additional complementary techniques to manage shared cache and shared DRAM subsystems. Temporal isolation is sometimes combined with spatial isolation to improve resource sharing and utilisation while reducing interference. Below, we subdivide the literature depending on how access to the memory bus is controlled, via (i) phased execution, (ii) memory bandwidth regulators, (iii) offline scheduling, and (iv) hardware isolation (e.g., a TDMA bus).

#### 3.1 Phased Execution Model

Research papers in this sub-category re-factor the tasks' code to create a new equivalent task with two types of disjoint phases: memory bound phases and computation bound phases. Each task typically starts by executing a memory phase in which all of the data and instructions needed by the task are read from main memory and stored in local private memory (e.g., cache or scratchpad). The subsequent computation phase can then perform the actual computation of the task using data and instructions that are readily available in the private memory, without any need to access the interconnect or shared main memory. Optionally, some models add a further memory phase at the end of each task to write back the updated data into the main memory. The phased execution of tasks is typically used in conjunction with a scheduling algorithm that exploits the fact that access to the shared main memory and bus are only going to occur during the memory phases of the tasks. Therefore, the scheduler can avoid contention in the main memory by not overlapping memory phases on different cores. Such a schedule can be achieved, for example, by defining a global scheduler with a queue just for memory phases.

An initial relevant implementation of the phased execution concept can be found in the work of Pellizzoni et al. [97] in 2008. This paper presents a framework to schedule tasks taking into account contention in the shared memory induced by concurrent master I/O peripheral Direct Memory Access (DMA) transfers. The basic idea is to control when the peripherals can operate using special hardware called a *peripheral gate*. A *co-scheduling* algorithm is proposed that tracks the actual execution times of the tasks to determine their slack (difference to their execution time budgets). These dynamic slack times are used to open the peripheral gates, making sure that the slack times are always non-negative. Although the paper targets single-core systems, its concepts can be applied to multi-core systems.

In 2011, Pellizzoni et al. [96] expanded the above ideas to define the PRedictable Execution Model (PREM). Under PREM, periodic tasks are decomposed into so-called predictable intervals and compatible intervals. Compatible intervals are reserved for those sections of code that cannot be re-factored into memory/computation phases, mainly due to the inability at compile time to determine which memory regions are accessed. From a scheduling standpoint, compatible intervals are treated as memory phases, since they can incur accesses to the bus. Experiments on a prototype test-bed validate the theory. In particular, execution is highly predictable and the WCET of memory bound tasks is significantly reduced.

Later works extend the ideas of PREM. In 2012, Yao et al. [129] proposed Memory-Centric scheduling where *non-preemptive* memory phases are executed in defined time slots using a high-level coarse-grained TDMA schedule. The main idea behind the Memory-Centric approach is to promote the priorities of tasks that are in memory phases above those that are in execution phases. Fixed-priority partitioned scheduling of tasks is assumed, and is extended to include priority promotion for memory phases. Cache partitioning is assumed to avoid any intra-core evictions. The TDMA memory scheduling provides isolation and thus single-core equivalence. Hence, the response time analysis provided only needs to consider the tasks executing on the same core as the task under analysis. The approach is effective when tasks have a high memory demand, but not when the memory demand of the tasks is low.

A comparison of different algorithms to schedule tasks using PREM was presented by Bak et al. [14] in 2012. The comparison is based on simulations performed on synthetic task sets, with different combinations of TDMA and priority-based schedulers for the memory and computation phases. The authors conclude from the simulated scenarios that the best policy is to schedule the computation phases with EDF, and the memory phases in a least-laxity-first non-preemptive manner. The simulations confirm the benefits of the priority promotion of the memory phases over the computation phases, as was also shown analytically by Yao et al. [129].

In 2014, Alhammad and Pellizzoni [4] proposed an offline static scheduling approach leveraging PREM. This work assumes a multi-core system with private LLC, or a partitioned shared cache. A static schedule of the memory and computation phases is constructed such that concurrent accesses to the shared memory are avoided. This eliminates delays due to concurrent accesses reducing WCETs. Later in 2014, Alhammad and Pellizzoni [3] extended PREM to global non-preemptive scheduling (called gPREM). Under gPREM, a task can only run when no other task is executing its memory phase and at least one processor is idle. This scheduling algorithm ensures that only one memory phase is executed system-wide. Contrary to the memory-centric approach of Yao et al. [129], no priority promotion of memory phases is implemented.

Also in 2014, Wasly and Pellizzoni [125] proposed a mechanism to partially hide the overheads induced by the memory phases by splitting the local double-ported memory into two partitions. The scheduling algorithm then ensures that, while a task is executing out of one local partition, the code and data for the next task to execute is placed in the *other* partition. A variation on fixed-priority non-preeemptive scheduling is assumed. The policy divides time into intervals, with scheduling decisions only made at the start of an interval. At the start of an interval, the processor executes the ready task that was loaded into one of the partitions before the end of the previous interval. The interval ends once both task execution and DMA operations have completed. An upper bound worst-case response time analysis is presented for the scheduling policy. The evaluation is performed using a custom scratchpad controller that implements the required latency-hiding capabilities. The paper assumes isolation at the bus level (e.g., TDMA arbitration in the memory bus). An extension of this work for global scheduling, that does not assume isolation through TDMA, was presented by Alhammad et al. [5] in 2015. In 2016, Tabish et al. [122] also reused this work and combined it with another set of isolation mechanisms (core private scratchpads, dedicated DMA channel using a TDMA schedule) to obtain predictable execution of an OS on a multi-core platform.

In 2014, Kim et al. [74] presented a method to construct offline (static) schedules of Integrated Modular Avionics (IMA) partitions for a multi-core system, with the objective of avoiding conflicts in I//O transactions. Each application is divided into three sequential non-preemptive phases: (i) device input, in which the input data of the device is copied into the main memory, (ii) processing of the data, and (iii) device output, in which the generated data is copied from the main memory to the output device. Each of these steps is executed as an IMA partition, and the I/O conflicts are avoided by executing the I/O partitions on a dedicated I/O core, which avoids overlapping I/O partitions. The paper presents a scalable heuristic to calculate the static schedule to meet the deadline and precedence constraints of the partitions. A previous work was presented in 2013 by the same authors [75] in which the I/O phases can be mapped to any core, so the concept of defining an I/O core is not used. The authors find this generalized problem to be NP-complete, and propose two solutions. The first is solved with Constraint Programming, and has the restriction that partitions mapped to the same core in the initial single-core system must be mapped to the same core in the final multi-core system. The second solution relaxes this restriction, but restricts the I/O phases to have a unitary length.

In 2015, Melani et al. [85] analytically characterised the improvements that can be achieved by a phased execution scheme for global fixed task priority scheduling. The paper proposes the first *exact* schedulability test for this model, and concludes that EDF is not optimal in this case. This work also provides and proves correct the critical instant for phased execution and defines an exact worst-case response time analysis for fixed-priority scheduling.

The Memory-Centric scheduling approach [129] was extended to global scheduling in 2016 by Yao et al. [130] without relying on TDMA to schedule the memory phases. This work uses the concepts of virtual memory cores, and virtual execution cores. The idea is to limit the number of cores that can access memory at the same time, ensuring that the memory bandwidth is not saturated

and the interference due to memory contention remains very small. A global fixed-priority scheduler is used. The priorities of the memory phases are promoted over that of the execution phases of all tasks. Only the  $m_{memo}$  highest priority ready tasks in memory phases are permitted to execute at any given time. Other ready tasks in memory phases are blocked. Schedulability analysis is provided, which effectively assumes that the memory phases run on  $m_{memo}$  cores and the execution phases run on the remaining cores. Evaluation shows that the approach outperforms a baseline (considering contention) when the slowdown of the latter due to memory contention is large.

In 2018, Pagetti et al. [93] proposed a compilation framework that extends the WCET-aware compiler (WCC) to also generate a mapping and a partitioned non-preemptive schedule. The execution model considered aims at eliminating interference by splitting tasks into sub-tasks representing data acquisition, execution, and replication phases. Moreover, the platform considered has a TDMA bus. Considering constraints from applications and platform descriptions, the framework uses an ILP solver to generate an offline schedule of tasks mapped to each core.

# 3.2 Memory Bandwidth Regulators

Research papers in this sub-category consider systems where access to the memory bus is restricted. Since memory bus accesses (e.g., LLC misses) can occur at any point in task execution, control over access to the memory bus is achieved by implementing a *memory bandwidth regulator*, which operates in a similar way to a periodic server: each core is assigned a portion of the total memory bus bandwidth in terms of a budget, which is replenished periodically. When a core exhausts it memory bus bandwidth, then it is idled until the start of its next period. The effect of implementing a memory bandwidth regulator is that the interference from other competing cores can be easily bounded. Additionally, by assigning budgets that avoid overloading the memory bus, each task runs with a guaranteed memory bandwidth that effectively ensures that its execution is *independent* of the behaviour of the tasks running on the other cores. Thus, timing analysis for single-core systems can be adapted to the case of multi-core systems with memory bandwidth regulation.

In 2012, Yun et al. [135] (reviewed in Section 4.1) proposed memory regulation similar to the behaviour of a periodic server. Subsequently, in 2013, they introduced MemGuard [136], which provides synchronous (same period) regulation of all cores via performance counter overflow interrupts.

In 2013, Behnam et al. [16] presented the Multi-Resource Server (MRS). These servers regulate both the processing time and memory bandwidth. When any budget in the server is depleted, the server is stalled until its next replenishment period. The proposed analysis is based on a compositional framework. It performs a local analysis of the tasks within a server, and also validates the set of servers globally. The analysis has the important simplifying assumption that memory access delays are considered *constant*. This limitation was later lifted by Inam et al. [61] in 2015. Here, a global upper bound for DRAM latencies with First-Ready FCFS (FR-FCFS) arbitration is calculated and used, with different delays for private and shared memory banks taken into account. The analysis considers the worst case by assuming that tasks deplete the memory budget by issuing sequential memory requests at the beginning of the server period.

In 2014, Nowotsch et al. [90] introduced an interference-aware WCET analysis, coupled with runtime monitoring and enforcement. The schedule is assumed to be offline (static) and time-triggered (ARINC 653 standard). The WCET is composed of two parts: the core-local execution time assuming privileged access to shared resources, and an upper bound on the shared resource interference delay. This upper bound is guaranteed by the Operating System, which monitors resource usage and prevents execution if the resource budget is going to be exceeded. This way a limited form of temporal isolation is guaranteed. The authors describe under what circumstances a simple summation of the interference delay and core-local execution time results in a safe upper

bound. Nowotsch et al. [89] extended their prior work [90]<sup>5</sup> by implementing a budget (i.e., capacity) re-claiming method. When a task exhausts its assigned capacity, the capacity usage of all the tasks is re-evaluated to determine if the suspended task can be granted some additional capacity to resume execution. As with the budget reclamation mechanisms implemented in Memguard [136], this approach aims at improving the average case while still providing a worst-case guarantee.

In 2015, Yao et al. [131] presented a WCET and schedulability analysis for multi-core systems with memory bandwidth regulators. Here, each core has a memory bandwidth budget (i.e., memory access time allowed per period) and a replenishment period. Cache is considered private or partitioned for each core. This work assumes a known WCET for each task running alone, and that this WCET can be divided into computation and memory access times. The analyses presented are based on the calculation of the stall time for the task under analysis, which can result from bandwidth regulation or from contention from other cores. One memory access can suffer interference at most once from each core. The stall time of the task under analysis is thus shown to be independent of the characteristics of the other tasks, thus achieving isolation via software means. For the WCET analysis proposed (which considers a task running alone in a core, but suffering interference from other cores), the authors show that tighter results can be obtained if the memory bandwidth replenishment periods of the cores are synchronised. The schedulability analysis is constructed by creating a synthetic task that includes the effects of all task instances in the relevant response-time analysis window. As a consequence, the WCET analysis can be applied to this synthetic task to obtain schedulability results. We note that this work considers a single constant memory access time. Subsequent work by Awan et al. [12] in 2018 extended the analysis from one to two memory controllers.

In 2015, Mancuso et al. [83] presented the Single-Core Equivalence (SCE) framework, which provides a means of *isolation*, effectively exporting a set of equivalent single-core machines to the application. SCE methods are applied to the LLC, DRAM memory bandwidth, and shared DRAM banks. Profiling is used to determine the pages of each task's code that have the most impact on the WCET and these pages are locked in the cache, thus avoiding any cross-core contention. The *Memguard* [136] mechanism is used to regulate the memory bandwidth allocation for each core in a given period. Thus, once the capacity is reached in terms of the number of accesses, the core is idled until the next server period. Finally, the *PALLOC* tool [133] is used to assign disjoint sets of DRAM banks to applications running on different cores to exploit parallel accesses. The additional latency due to memory regulation is integrated into response time analysis assuming that memory bandwidth is equally distributed among the cores. Note, in contrast to the work of Yao et al. [131], this work considers minimum and maximum memory access latencies.

Also in 2016, Pellizzoni and Yun [99] presented a schedulability analysis for memory bandwidth regulated systems with FR-FCFS memory arbitration. The analysis exploits knowledge of the restrictions on memory requests from competing cores to produce lower delay bounds. First, it performs a core-local analysis to determine the bandwidth requirements that a core needs to schedule its tasks. These requirements are called the schedulability envelope, and are defined as the memory budget required by the core, and the maximum memory budget that can be assigned to other cores. Second, a system analysis is performed to determine if the demands of all cores can be satisfied. The benefit is that each core can be developed independently, with no knowledge of the tasks running on the other cores. The authors define separate analyses for systems with read only regulation, and for systems with read/write regulation.

In 2017, Mancuso et al. [84] extended the SCE approach based on Memguard [136], allowing different memory bandwidth budgets for the different cores. This work shows how to derive task

<sup>&</sup>lt;sup>5</sup>Note that although [90] was published after [89] it contains earlier work and is cited in [89].

WCETs as a function of the assigned memory budget, the execution time (not including memory requests), and the number of memory requests. Schedulability analysis is then given that utilises these WCET functions. The evaluation shows around 30% improvement in WCET compared to assigning equal budgets to all cores.

In 2017, Agrawal et al. [1] tackled the problem of scheduling ARINC 653 partitions in a multi-core system taking into account memory contention. The computation and memory access budgets are given at the slot level instead of the partition level. Memory budgets for each slot are selected from a list of pre-defined budgets that depend on how many cores are active in the slot (when more cores are active then each core is given a lower memory budget). The offline (static) schedule and slot budget assignments are performed using an upper bound on the number of memory accesses for each partition and a WCET for execution in isolation. The worst-case memory access pattern is constructed by moving the memory accesses to the slots with lower memory budgets.

In 2018, Agrawal et al. [2] considered the case where the core memory bandwidth budgets can change arbitrarily over time. The analysis is constructed as an optimisation problem that aims to find the worst-case memory request distribution for each budget configuration. The evaluation is performed on an ARINC 653 type system. It shows that dynamic budget assignments dominate static budget assignments for the task sets studied. A simple heuristic is also provided to calculate dynamic and static budget distributions.

In 2018, Awan et al. [13] extended the SCE approach considering uneven memory regulation (assuming upper and lower bounds on the access time of a single memory transaction). The idea being to provide inter-server isolation even for servers on the same core. The budget assignment is obtained by solving an ILP system of constraints. The results show an improvement in terms of schedulability over previous approaches.

In 2018, Freitag et al. [41] presented an isolation technique using performance counters. The isolation proposed here differs from other works on memory bandwidth regulation in that one core is given priority over all others. Real-time guarantees can therefore only be provided for this dedicated real-time core, whereas all other cores are effectively executing tasks on a best-effort basis. Performance counters are used to track the progress of the real-time application on the dedicated core. As soon as the performance falls behind the statically predicted necessary progress to finish on time, other cores are either slowed down, or halted entirely to reduce the memory contention.

#### 3.3 Offline Scheduling

Research papers in this sub-category use offline static scheduling techniques whereby a table is generated that contains all of the scheduling decisions for use at runtime such that concurrent accesses to shared resources (e.g., the memory bus) are controlled.

In a series of papers [43–45] from 2013 to 2016, Giannopoulou et al. build on top of non-preemptive Flexible Time-Triggered Scheduling (FTTS) with dynamic barriers to achieve partial isolation in a mixed-criticality system. The initial work [43] in 2013 considers offline scheduling and task mapping to cores, accounting for processing time and synchronous memory accesses, while ensuring co-ordination among cores such that tasks of different criticality levels are not executed at the same time. Simulated annealing algorithms are proposed for the task mapping and construction of the schedule. Worst-case response time analysis accounting for synchronous memory accesses is done via the Timed Automata and model checking methods described in [42]. Later work [44] in 2014 further develops the system design optimisation under FTTS for memory bank sharing. A simulated annealing framework is used to map tasks to cores, and data and communication buffers to shared memory banks. Finally, a further generalisation in 2016 [45] considers scheduling and task/memory mapping for a *clustered many-core* system taking into account delays

due to memory banks local to the cluster and due to remote data copied from external memory. Task dependencies are supported, and tasks are also assumed to have a minimum degraded execution requirement that must be satisfied in all system criticality levels. Network calculus is used to bound the delays over the NoC, while task mapping to cores and shared memory mapping to local memory banks is optimised using a simulated annealing algorithm.

In 2016, Perret et al. [102] introduced an execution model that restricts the application behaviour to ensure temporal and spatial isolation between applications and to bound the WCET. The execution model consists of a set of rules that include spatial partitioning of the tasks, time-driven access to the NoC, and rules to share the DDRx-SDRAM banks.

In 2015, Carle et al. [19] proposed an automatic procedure for the design and implementation of dataflow programs on multiprocessors. Here, a task allocation algorithm is used to optimise the end-to-end response time. Temporal isolation is enforced between tasks allocated to different time frames, while a conservative upper bound on the WCETs accounts for all delays due to accesses to shared resources by tasks in the same time frame.

In 2018, Carle and Cassé [18] presented a method to derive a static schedule of unmodified binaries that minimise the execution time inflation due to inter-core interference. The standard IPET WCET technique is used to identify which instructions in the binary code are not guaranteed to always be cache hits and thus could suffer from interference. These instructions are called TIPs (Time Interest Points). Tasks are represented by a sequence of intervals, each with a constant execution time, separated by TIPs. A partial isolation approach is proposed. This involves building a static schedule using ILP that minimises interference, considering a constant cost per interference. The authors conclude that with this approach ILP is only applicable for relatively short tasks.

Research that makes use of offline (static) scheduling for the purposes of temporal isolation but is reviewed elsewhere in this survey includes the work of Alhammad and Pellizzoni [4] (see Section 3.1) and Becker et al. [15] (see Section 5.1).

#### 3.4 Hardware Isolation

Research papers in this sub-category focus on WCET analysis in the context of hardware isolation mechanisms where interference either does not depend on the co-runners, or can be bounded independent of the behaviour of the co-runners. A TDMA or Round-Robin bus arbiter is the most popular way to ensure such hardware isolation; other approaches use memory partitioning/optimisation.

In 2007, Rosèn et al. [105] proposed an approach that integrates system-level static cyclic scheduling and WCET analysis. The main focus is on optimising the periodic schedule table of TDMA slots that give each core access to the bus, with the aim of minimising the latest termination time of a set of tasks represented by a task graph. A system-level offline (static) schedule of tasks (executing on all cores) is constructed using a list scheduling approach. At each step, corresponding to the start of a task, the next segment of the bus schedule (up to the next completion of a task) is optimised according to a cost function that considers the WCETs of the currently active tasks and an estimate based on the conflict-free WCET of their successors. (Note the WCETs of the active tasks are dependent on the bus schedule and are recomputed for the different bus schedules examined as part of this optimisation step). Each WCET computation uses an ILP system that encodes accesses and the availability of the bus.

In a paper in 2011 [66], and the extension to it in 2014 [67], Kelter et al. presented WCET analysis in the context of multi-core systems with local instruction and data scratchpads connected via a shared TDMA bus to a global shared memory. The analysis takes the precise time offset between task execution and TDMA slots into account to bound the delay each memory access may suffer while waiting for the next TDMA slot. The analysis operates at the level of basic-blocks and

formulates an offset graph that captures the dependencies between different memory accesses (i.e., the impact that delays to an earlier access can have on the timing of subsequent accesses). The offset graph is used to encode the timing dependencies into an ILP system of constraints, and thus determine the WCET.

In 2011, Yoon et al. [132] introduced a WCET estimation depending on cache partitioning and bus configuration. The solving of a Mixed Integer Linear Programming (MILP) system of constraints leads to a WCET estimation and cache and bus configuration. The WCET estimation is separated into a local WCET estimation that does not depend on other cores or tasks, and an interference delay. For the bus, a configurable Round-Robin scheme is used where each core has an upper bound on the delay and different "rounds" are defined. For the cache, the notion of banks and columns are used to partition.

In 2013, Kelter et al. [68] derived formulae for the bounds on the worst-case bus access delay for four bus arbitration policies: Round-Robin, TDMA, priority division, and priority-based arbitration. They also compared the worst-case and average-case performance of these schemes. Building on this earlier work, in 2014 Kelter et al. [65] investigated two techniques to reduce WCETs in partitioned multi-core systems. First, they use a genetic algorithm to optimise the bus schedule (i.e., the number of slots and their length, assigned to each core) for a set of bus arbitration policies, including Round-Robin, TDMA, and priority-based. Second, they explore reordering instructions within basic blocks to better match the bus schedule. (The WCET bounds for each bus arbitration policy are estimated using the formulae from [68]). Overall, an improvement of up to 33% is observed. This technique also allows a tradeoff between average-case and worst-case execution time.

A framework for memory contention analysis was introduced by Dasari et al. [35] in 2015. The focus of this work is on the shared resource access delay, with an upper bound on the number of accesses assumed to be provided for each task. (In the paper, this upper-bound is obtained from measurements, with regions of task execution used for a more fine-grained analysis). The shared bus arbiter is modelled by considering the earliest and latest available communication slots for the task under analysis. Mathematical models of the most widely used bus arbiters are provided. This work was extended by Dasari et al. [36] in 2016, considering cache partitioning to provide better isolation and hence obtain more precise timing bounds. The aim of the work is then to compute the WCETs of the tasks (executing concurrently) assuming specific bus policies, both work-conserving and non-work-conserving (e.g., TDMA), and fixed-priority partitioned scheduling.

In 2016, Valsan et al. [123, 124] showed that partitioning the shared cache in COTS multi-core processors that use non-blocking caches is not enough to ensure predictable execution time behaviour. (Non-blocking caches allow hits to still be served from the cache, while waiting for a miss to be served from main memory). The authors showed for three different COTS multi-core architectures that even when the global (LLC) cache is partitioned between cores, co-runners can cause up to a 21-fold increase in execution times compared with running alone. This is due to contention over Miss Status Holding Registers (MSHR). A combined hardware and software solution is presented that controls the memory-level parallelism of each core and eliminates contention over MSHRs.

In 2017, Oehlert et al. [92] proposed an ILP formulation for WCET estimation and a Genetic Algorithm for selecting code to place in local scratchpad memory so as to reduce the WCET. This work is in the context of TDMA bus arbitration. In particular, the stall delays due to the TDMA cycle influence the optimal scratchpad allocation. The bus-aware approach that the authors propose is evaluated against a similar bus-unaware approach. For a dual-core, the new ILP method gives 23% lower WCET estimates on average, while the genetic algorithm resulted in higher WCETs. These results were more pronounced for more cores due to the longer bus stall times.

Research that overlaps with this sub-category but is reviewed elsewhere in this survey includes the work of Lv et al. [82] (see Section 2.1), Rihani et al. [103] (see Section 2.2), Andrei et al. [10] (see Section 2.3), Suhendra et al. [121] and Chattopadhyay and Roychoudhary [25] (see Section 4.2), and Schranzhofer et al. [112] (see Section 4.1).

#### 3.5 Critique and Perspectives

Research in this category relies on mechanisms that shape access to shared hardware resources, particularly the interconnect/memory bus, reducing or preferably eliminating contention. This shaping makes the system more predictable and greatly simplifies the analysis needed for timing verification. There are, however, a number of tradeoffs.

Research in the first sub-category makes use of the *phased execution model*, which only allows a limited number of memory phases at the same time, usually only one, thus providing temporal isolation. Here the tradeoffs include (i) the code overheads added by the memory phases and (ii) the delays until the scheduler grants each memory phase access to the bus.

Research in the second sub-category makes use of *memory bandwidth regulators*. The main tradeoff of this approach is that regulation effectively *slows down* task execution, with each task running as if the memory bus was always just below its saturation point, even when other cores are idle. This leads, in many cases, to not fully utilising the computing resources of the platform.

Research in the third sub-category makes use of *offline scheduling* to shape accesses and hence provide temporal isolation. As with single-core systems, a lack of flexibility is the main tradeoff for the high degree of predictability afforded by offline schedules. The system configuration may need to be completely re-computed for every change in the set of tasks.

Research in the fourth sub-category makes use of *hardware isolation* to shape accesses. The difficulty here is that hardware isolation techniques necessarily require specific hardware designs to be employed. Often hardware isolation, for example via a TDMA bus, comes at a cost in terms of using non-work-conserving protocols that compromise the effective bandwidth that can be used. As a result, such techniques are rarely employed in COTS multi-core systems. Partial isolation using arbitration policies such as Round-Robin means that interference can be bounded independent of the co-runners; however, typically the analysis is more pessimistic since a worst-case delay is assumed on every access.

In conclusion, the research described in this section shows that while techniques based on the concept of temporal isolation can lead to more predictable access to shared hardware resources and consequently simpler analysis for timing verification, the main tradeoff is in not fully taking advantage of the system computing resources (i.e., compromising throughput and average case performance). An open question is whether temporal isolation techniques and their analyses can be improved to allow better utilisation of the available hardware resources. The work of Hebbache et al. [58] in 2018 on dynamic bus arbitration schemes based on TDMA is an example of research in this direction. The approach proposed provides utilisation similar to that of work-conserving policies, while preserving the guarantees of TDMA in the worst-case.

## 4 INTEGRATING INTERFERENCE EFFECTS INTO SCHEDULABILITY ANALYSIS

Research in this category aims to account for additional delays that impact task execution due to the arbitration policies used to access shared resources and the contention caused by co-running tasks on other cores. It does so by integrating these delays into *schedulability analysis*. Typically, the WCET for each task running in isolation (i.e., without contention for resources) is used as a baseline, with the effects of contention included as additional terms in the *response time analysis* or other schedulability test formulation. Many works consider a single shared resource such as the interconnect or memory bus, shared cache, or DRAM, while other papers integrate the effects

of contention across multiple shared resources. Below, we subdivide the literature depending on the interference considered: (i) interference contending for the memory bus, (ii) interference contending for memory (cache, scratchpads, or DRAM), and (iii) interference contending for multiple resources.

## 4.1 Interference Contending for the Memory Bus

Research papers in this sub-category focus mainly on analysing contention on the memory bus and how the effects of this can be integrated into schedulability analysis.

In a series of papers [107–110] from 2008 to 2011, Schliecker et al. considered the effect of resource accesses delays, due to co-runner contention, on the response times of tasks. The state-of-the-art for this thread of research is captured in the final paper [107], which generalises the approach to arbitrary shared resources with work-conserving arbitration policies. Schliecker and Ernst [107] use arrival curves to model the number of resource accesses from each task, using a minimum separation between accesses and a maximum number of accesses per job. This is extended to multiple tasks running on a single core. For each task, its WCRT is computed based on the task's baseline WCET (assuming no resource access delays), preemptions due to higher priority tasks on the same core, and delays due to accesses by the task itself, higher priority tasks on the same core, and also accesses due to tasks on other cores in the same time window. The overall framework uses an outer fixed point iteration to handle the dependencies between the WCRTs of tasks on different cores. The evaluation examines the performance of different types of interconnect, including a cross-bar, a FCFS bus, and a FCFS bus that supports two accesses in parallel. It shows that the proposed approach is much less pessimistic than assuming the worst-case delay for every bus access that a task makes.

Schranzhofer et al. published a series of three papers [112–114] during 2010 and 2011 based on the *superblock* model. In this model, each task is represented by a sequence of superblocks, which may have branches and loops within them. The task set is assumed to be periodic and all execution on a core is assumed to be described by a sequence of superblocks (i.e., an offline static cyclic schedule). The first paper [112] considers TDMA bus arbitration. The second paper [113] provides worst-case completion time analysis for the superblocks and hence a schedulability test. It covers three models: (i) arbitrary memory accesses anywhere in the superblocks, (ii) dedicated phases where accesses only occur at the start and end of each superblock, and (iii) a hybrid where most accesses are in the acquisition and replication phases, but some accesses can take place in the intervening execution phase. The conclusion is that the dedicated model improves schedulability due to less contention. The third paper [114] extends the approach to an adaptive bus arbiter with both static and dynamic segments. The method uses a dynamic programming technique to compute the minimum amount of execution of a superblock that must have taken place to reach a particular frame in the arbitration schedule, considering the interference due to requests from tasks executing on other cores. The task WCRTs are then computed from this information.

In 2010, Pellizzoni et al. [98] also considered the superblock model. They assume that the maximum number of memory accesses made by an individual task (or by a set of tasks) in a given time interval can be upper bounded by an arrival curve. They derive arrival curves for both un-buffered accesses from a task that stalls waiting on the request and buffered accesses from DMA. A dynamic programming technique is then used to compute the maximum interference on the memory requests of a given task, and hence the worst-case delays due to memory bus interference under Round-Robin, fixed-priority, or TDMA bus arbitration.

In 2012, Giannopoulou et al. [42] proposed a state-based response-time analysis based on Timed Automata for multi-core systems using the superblock model. They model superblocks, static schedulers for the cores, and resource arbiters as Timed Automata with analysis provided via

model checking. To improve scalability, each core is analysed separately, with interference from other cores abstracted via arrival curves.

Lampka et al. [77] published another paper using the superblock model in 2014. The approach in this paper relies on model checking and abstract interpretation combined with Real-Time Calculus. The aim here is to provide an upper-bound on the worst-case response time of concurrent tasks considering contention on shared memory. The authors first propose a method based on timed automata to precisely model the applications, the scheduler, shared resource accesses, and the arbitration policy used in the shared memory bus. Arbitration policies considered are Round-Robin, FCFS, and TDMA. The scalability of WCRT analysis is enhanced by abstracting the concurrent accesses to the shared resource with arrival curves from Real-Time Calculus.

In 2011, Dasari et al. [33] presented a response-time analysis for partitioned tasks scheduled using fixed-priority non-preemptive scheduling on a multi-core with a shared memory bus, which utilises a work-conserving arbitration policy. The bus contention from each task is modelled via a request function that returns the maximum number of bus requests that can be made by the task in a given time interval. The request function is computed by examining all paths through the code of the task and determining the pattern of accesses. Alternatively, it can be estimated via measurements using performance counters. The request function is integrated into schedulability analysis as an additional term in the WCRT equations. Since the request function for each task depends on the task's WCRT, an outer fixed point iteration is made over all tasks, until all response times converge to fixed values or a deadline is exceeded.

In 2012, Yun et al. [135] proposed a software method to control resource contention on a shared memory bus on COTS multi-cores. This work assumes a dedicated core which executes all critical real-time tasks. Contention due to tasks running on other cores is then limited by memory throttling. The idea is to set a budget of Q bus requests in any period P. If this budget is exceeded, as checked via performance counters, then the tasks on the non-critical core(s) are suspended until the period ends. The budget may be applied statically to individual cores or dynamically to a group of non-critical cores. The authors show how to incorporate an extra interference term into standard response time analysis to account for the interference from other cores. This term is limited via the parameters of the memory throttling. The evaluation shows that the dynamic approach is more effective and provides the non-critical cores with better performance, as they are throttled for less time.

## 4.2 Interference Contending for Memory

Research papers in this sub-category focus mainly on analysing contention over shared cache, while other works consider scratchpad memories and DRAM.

An allocation algorithm for placing instructions into local scratchpads and shared memory to reduce the WCET in multi-core systems was proposed by Suhendra et al. [121] in 2010. This algorithm also calculates scratchpad re-loading points to leverage the memory requirements of tasks with disjoint lifetimes. Each task can only access its own local scratchpad, and the latency of any access to memory (scratchpad or main memory) is considered bounded by a constant. This work also includes a response-time analysis that takes into account the scratchpad allocation.

In 2011, Chattopadhyay et al. [25] presented an algorithm to allocate (at compile time) data variables into scratchpad and global shared memory in order to minimize the WCRT of the tasks. They provide a response-time analysis that considers a scratchpad allocation, assuming an architecture where each core has a local scratchpad, and all scratchpads can be joined to form a virtual scratchpad space accessible by any core. The proposed allocation takes into account the delays to access the shared memory via a TDMA bus.

In 2009, Guan et al. [48] presented a cache-aware global fixed-priority non-preemptive scheduling policy for multi-core systems with a shared L2 cache that can be partitioned at the level of cache blocks. When a core is idle, the policy selects the highest priority ready task to execute; however, the task only runs if sufficient L2 cache blocks are available, hence the policy is not work-conserving. The authors note that allowing lower priority tasks requiring fewer blocks to run ahead of higher priority tasks (i.e., making the policy work-conserving) could result in unbounded blocking. They present two schedulability tests for the policy, one which uses a Linear Programming formulation, and a second which uses a closed- form approximation. Evaluation shows that the second test has good performance, similar to the first.